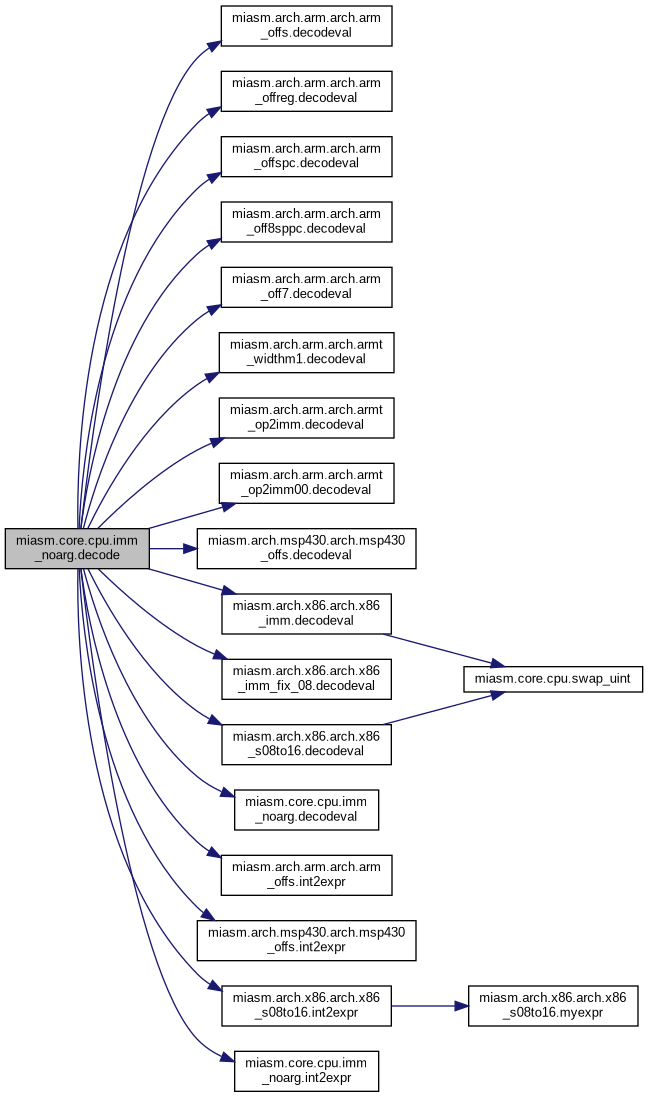

◆ decode()

| def miasm.core.cpu.imm_noarg.decode |

( |

|

self, |

|

|

|

v |

|

) |

| |

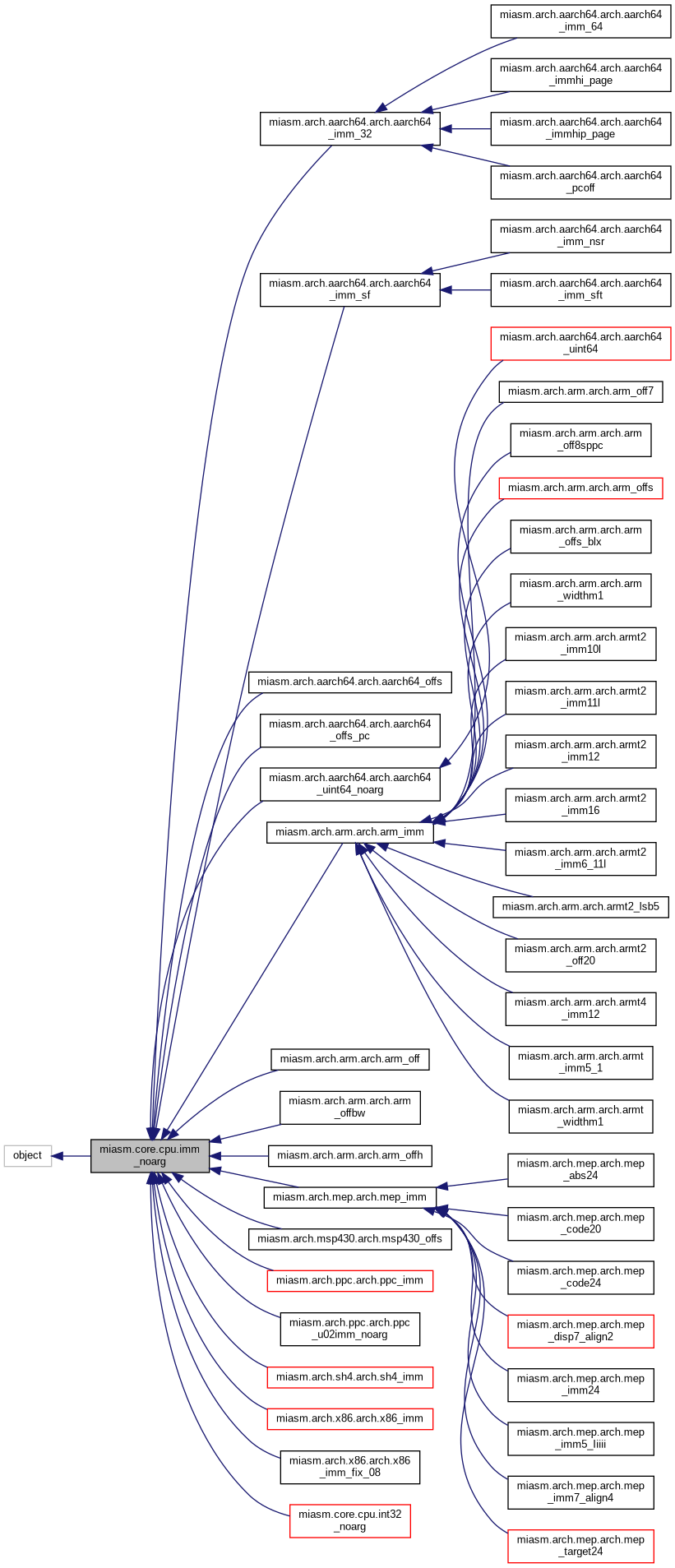

Reimplemented in miasm.core.cpu.int32_noarg, miasm.arch.x86.arch.x86_s08to32, miasm.arch.x86.arch.x86_s08to16, miasm.arch.x86.arch.x86_08_ne, miasm.arch.sh4.arch.sh4_simm, miasm.arch.ppc.arch.ppc_tbr, miasm.arch.ppc.arch.ppc_spr, miasm.arch.ppc.arch.ppc_u16imm, miasm.arch.ppc.arch.ppc_s16imm, miasm.arch.ppc.arch.ppc_s24imm_branch, miasm.arch.ppc.arch.ppc_s14imm_branch, miasm.arch.msp430.arch.msp430_offs, miasm.arch.mep.arch.mep_abs24, miasm.arch.mep.arch.mep_imm24, miasm.arch.mep.arch.mep_disp12_align2_signed, miasm.arch.mep.arch.mep_disp7_align2, miasm.arch.mep.arch.mep_imm5_Iiiii, miasm.arch.mep.arch.mep_imm7_align4, miasm.arch.mep.arch.mep_code24, miasm.arch.mep.arch.mep_code20, miasm.arch.mep.arch.mep_target24_signed, miasm.arch.mep.arch.mep_target24, miasm.arch.arm.arch.armt_imm5_1, miasm.arch.arm.arch.armt2_imm6_11l, miasm.arch.arm.arch.armt2_imm11l, miasm.arch.arm.arch.armt2_imm10l, miasm.arch.arm.arch.armt2_off20, miasm.arch.arm.arch.armt2_lsb5, miasm.arch.arm.arch.armt2_imm16, miasm.arch.arm.arch.armt4_imm12, miasm.arch.arm.arch.armt2_imm12, miasm.arch.arm.arch.arm_offh, miasm.arch.arm.arch.arm_off, miasm.arch.arm.arch.arm_offbw, miasm.arch.arm.arch.arm_widthm1, miasm.arch.arm.arch.arm_offs_blx, miasm.arch.arm.arch.arm_offs, miasm.arch.aarch64.arch.op0_value, miasm.arch.aarch64.arch.aarch64_offs_pc, miasm.arch.aarch64.arch.aarch64_offs, miasm.arch.aarch64.arch.aarch64_immhi_page, miasm.arch.aarch64.arch.aarch64_immhip_page, miasm.arch.aarch64.arch.aarch64_imm_nsr, miasm.arch.aarch64.arch.aarch64_imm_sft, and miasm.arch.aarch64.arch.aarch64_imm_sf.

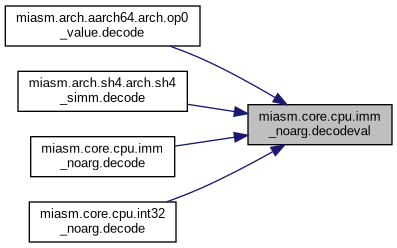

◆ decodeval()

| def miasm.core.cpu.imm_noarg.decodeval |

( |

|

self, |

|

|

|

v |

|

) |

| |

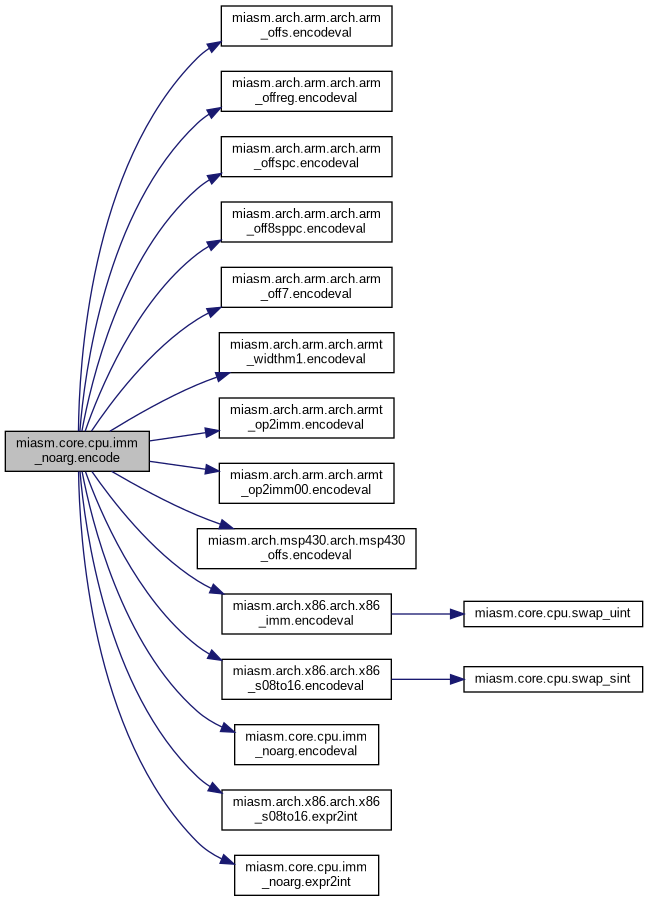

◆ encode()

| def miasm.core.cpu.imm_noarg.encode |

( |

|

self | ) |

|

Reimplemented in miasm.core.cpu.int32_noarg, miasm.arch.x86.arch.x86_s08to16, miasm.arch.x86.arch.x86_08_ne, miasm.arch.x86.arch.x86_imm_fix_08, miasm.arch.sh4.arch.sh4_simm, miasm.arch.ppc.arch.ppc_u16imm, miasm.arch.ppc.arch.ppc_s16imm, miasm.arch.ppc.arch.ppc_s24imm_branch, miasm.arch.ppc.arch.ppc_s14imm_branch, miasm.arch.msp430.arch.msp430_offs, miasm.arch.mep.arch.mep_abs24, miasm.arch.mep.arch.mep_imm24, miasm.arch.mep.arch.mep_disp7_align2, miasm.arch.mep.arch.mep_imm5_Iiiii, miasm.arch.mep.arch.mep_imm7_align4, miasm.arch.mep.arch.mep_code24, miasm.arch.mep.arch.mep_code20, miasm.arch.mep.arch.mep_target24, miasm.arch.mep.arch.mep_int32_noarg, miasm.arch.arm.arch.armt_imm5_1, miasm.arch.arm.arch.armt2_imm6_11l, miasm.arch.arm.arch.armt2_imm11l, miasm.arch.arm.arch.armt2_imm10l, miasm.arch.arm.arch.armt2_off20, miasm.arch.arm.arch.armt2_lsb5, miasm.arch.arm.arch.armt2_imm16, miasm.arch.arm.arch.armt4_imm12, miasm.arch.arm.arch.armt2_imm12, miasm.arch.arm.arch.arm_offh, miasm.arch.arm.arch.arm_off, miasm.arch.arm.arch.arm_offbw, miasm.arch.arm.arch.arm_widthm1, miasm.arch.arm.arch.arm_offs_blx, miasm.arch.arm.arch.arm_offs, miasm.arch.aarch64.arch.op0_value, miasm.arch.aarch64.arch.aarch64_offs_pc, miasm.arch.aarch64.arch.aarch64_offs, miasm.arch.aarch64.arch.aarch64_immhi_page, miasm.arch.aarch64.arch.aarch64_immhip_page, miasm.arch.aarch64.arch.aarch64_imm_nsr, miasm.arch.aarch64.arch.aarch64_imm_sft, and miasm.arch.aarch64.arch.aarch64_imm_sf.

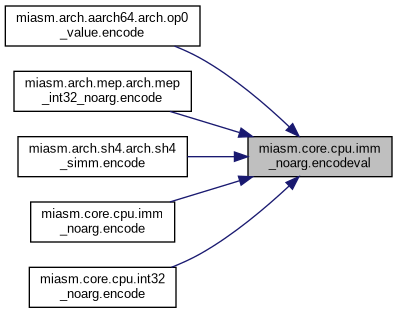

◆ encodeval()

| def miasm.core.cpu.imm_noarg.encodeval |

( |

|

self, |

|

|

|

v |

|

) |

| |

◆ expr2int()

| def miasm.core.cpu.imm_noarg.expr2int |

( |

|

self, |

|

|

|

e |

|

) |

| |

◆ fromstring()

| def miasm.core.cpu.imm_noarg.fromstring |

( |

|

self, |

|

|

|

text, |

|

|

|

loc_db, |

|

|

|

parser_result = None |

|

) |

| |

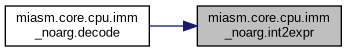

◆ int2expr()

| def miasm.core.cpu.imm_noarg.int2expr |

( |

|

self, |

|

|

|

v |

|

) |

| |

◆ expr

| miasm.core.cpu.imm_noarg.expr |

◆ intmask

| tuple miasm.core.cpu.imm_noarg.intmask = (1 << intsize) - 1 |

|

static |

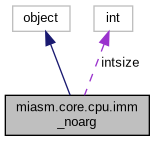

◆ intsize

| int miasm.core.cpu.imm_noarg.intsize = 32 |

|

static |

◆ value

| miasm.core.cpu.imm_noarg.value |

The documentation for this class was generated from the following file:

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/core/cpu.py