|

miasm

Reverse engineering framework

|

|

miasm

Reverse engineering framework

|

Functions | |

| def | cb_shift (tokens) |

| def | cb_extreg (tokens) |

| def | cb_shiftreg (tokens) |

| def | cb_shift_sc (tokens) |

| def | cb_extend (tokens) |

| def | cb_deref_pc_off (tokens) |

| def | cb_deref_pc_nooff (tokens) |

| def | cb_deref_nooff (t) |

| def | cb_deref_post (t) |

| def | cb_deref_pre (t) |

| def | cb_deref_pre_wb (t) |

| def | cb_deref_ext2op (t) |

| def | aarch64op (name, fields, args=None, alias=False) |

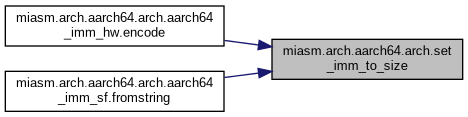

| def | set_imm_to_size (size, expr) |

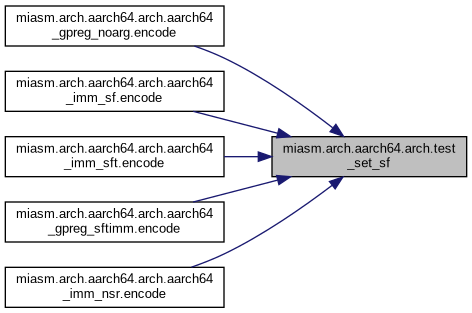

| def | test_set_sf (parent, size) |

| def | ror (value, amount, size) |

| def | rol (value, amount, size) |

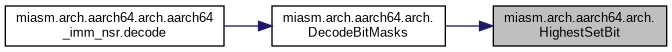

| def | HighestSetBit (x) |

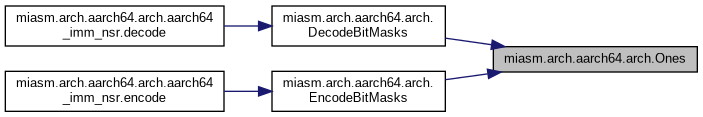

| def | Ones (N) |

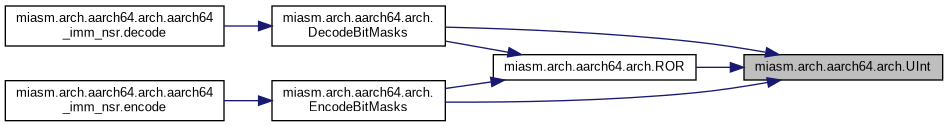

| def | ROR (x, shift) |

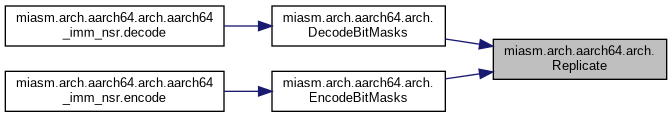

| def | Replicate (x, N) |

| def | UInt (x) |

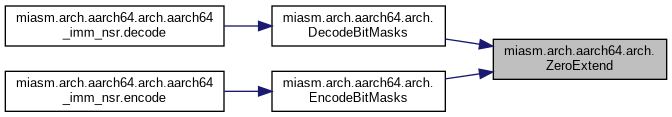

| def | ZeroExtend (x, N) |

| def | DecodeBitMasks (M, immN, imms, immr, immediate) |

| def | EncodeBitMasks (wmask) |

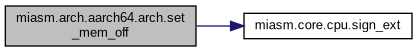

| def | set_mem_off (parent, imm) |

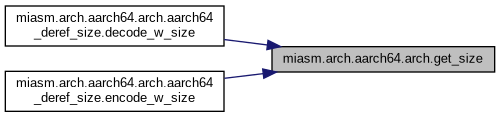

| def | get_size (parent) |

Variables | |

| log = logging.getLogger("aarch64dis") | |

| console_handler = logging.StreamHandler() | |

| dictionary | replace_regs |

| dictionary | shift2expr_dct = {'LSL': '<<', 'LSR': '>>', 'ASR': 'a>>', 'ROR': '>>>'} |

| list | shift_str = ["LSL", "LSR", "ASR", "ROR"] |

| list | shift_expr = ["<<", ">>", "a>>", '>>>'] |

| all_binaryop_lsl_t = literal_list(shift_str).setParseAction(cb_shift) | |

| all_binaryop_shiftleft_t = literal_list(["LSL"]).setParseAction(cb_shift) | |

| list | extend_lst = ['UXTB', 'UXTH', 'UXTW', 'UXTX', 'SXTB', 'SXTH', 'SXTW', 'SXTX'] |

| list | extend2_lst = ['UXTW', 'LSL', 'SXTW', 'SXTX'] |

| all_extend_t = literal_list(extend_lst).setParseAction(cb_extreg) | |

| all_extend2_t = literal_list(extend2_lst).setParseAction(cb_extreg) | |

| tuple | gpregz32_extend = (gpregsz32_info.parser + Optional(all_extend_t + base_expr)).setParseAction(cb_extend) |

| tuple | gpregz64_extend = (gpregsz64_info.parser + Optional(all_extend_t + base_expr)).setParseAction(cb_extend) |

| tuple | shift32_off = (gpregsz32_info.parser + Optional(all_binaryop_lsl_t + base_expr)).setParseAction(cb_shiftreg) |

| tuple | shift64_off = (gpregsz64_info.parser + Optional(all_binaryop_lsl_t + base_expr)).setParseAction(cb_shiftreg) |

| tuple | shiftimm_imm_sc = (base_expr + all_binaryop_shiftleft_t + base_expr).setParseAction(cb_shift_sc) |

| tuple | shiftimm_off_sc = shiftimm_imm_sc | base_expr |

| tuple | shift_off = (shift32_off | shift64_off) |

| tuple | reg_ext_off = (gpregz32_extend | gpregz64_extend) |

| tuple | gpregs_32_64 = (gpregs32_info.parser | gpregs64_info.parser) |

| tuple | gpregsz_32_64 = (gpregsz32_info.parser | gpregsz64_info.parser | base_expr) |

| tuple | simdregs = (simd08_info.parser | simd16_info.parser | simd32_info.parser | simd64_info.parser) |

| tuple | simdregs_h = (simd32_info.parser | simd64_info.parser | simd128_info.parser) |

| tuple | simdregs_h_zero = (simd32_info.parser | simd64_info.parser | simd128_info.parser | base_expr) |

| dictionary | gpregs_info |

| dictionary | gpregsz_info |

| dictionary | simds_info |

| LBRACK = Suppress("[") | |

| RBRACK = Suppress("]") | |

| COMMA = Suppress(",") | |

| POSTINC = Suppress("!") | |

| tuple | deref_nooff = (LBRACK + gpregs64_info.parser + RBRACK).setParseAction(cb_deref_nooff) |

| tuple | deref_off_post = (LBRACK + gpregs64_info.parser + RBRACK + COMMA + base_expr).setParseAction(cb_deref_post) |

| tuple | deref_off_pre = (LBRACK + gpregs64_info.parser + COMMA + base_expr + RBRACK).setParseAction(cb_deref_pre) |

| tuple | deref_off_pre_wb = (LBRACK + gpregs64_info.parser + COMMA + base_expr + RBRACK + POSTINC).setParseAction(cb_deref_pre_wb) |

| tuple | deref = (deref_off_post | deref_off_pre_wb | deref_off_pre | deref_nooff) |

| tuple | deref_pc_off = (LBRACK + Literal("PC") + COMMA + base_expr + RBRACK).setParseAction(cb_deref_pc_off) |

| tuple | deref_pc_nooff = (LBRACK + Literal("PC") + RBRACK).setParseAction(cb_deref_pc_nooff) |

| tuple | deref_pc = (deref_pc_off | deref_pc_nooff) |

| tuple | deref_ext2 = (LBRACK + gpregs_32_64 + COMMA + gpregs_32_64 + Optional(all_extend2_t + base_expr) + RBRACK).setParseAction(cb_deref_ext2op) |

| list | CONDS |

| list | CONDS_INV |

| list | BRCOND = ['B.' + cond for cond in CONDS] + ['CBZ', 'CBNZ', 'TBZ', 'TBNZ'] |

| conds_expr | |

| conds_info | |

| conds_inv_expr | |

| conds_inv_info | |

| list | OPTION2SIZE |

| dictionary | EXT2_OP |

| EXT2_OP_INV = dict((value, key) for key, value in viewitems(EXT2_OP)) | |

| modf = bs_mod_name(l=1, fname='modf', mn_mod=['', 'S']) | |

| sf = bs(l=1, fname='sf', order=-1) | |

| shift = bs(l=2, fname='shift') | |

| shiftb = bs(l=1, fname='shift', order=-1) | |

| rn64_v = bs(l=5, cls=(aarch64_gpreg64_nodec,), fname='rn', order=-1) | |

| rn = bs(l=5, cls=(aarch64_gpreg,), fname="rn") | |

| rs = bs(l=5, cls=(aarch64_gpreg,), fname="rs") | |

| rm = bs(l=5, cls=(aarch64_gpreg,), fname="rm") | |

| rd = bs(l=5, cls=(aarch64_gpreg,), fname="rd") | |

| ra = bs(l=5, cls=(aarch64_gpregz,), fname="ra") | |

| rt = bs(l=5, cls=(aarch64_gpregz,), fname="rt") | |

| rt2 = bs(l=5, cls=(aarch64_gpregz,), fname="rt2") | |

| rn0 = bs(l=5, cls=(aarch64_gpreg0,), fname="rn") | |

| rmz = bs(l=5, cls=(aarch64_gpregz,), fname="rm") | |

| rnz = bs(l=5, cls=(aarch64_gpregz,), fname="rn") | |

| rdz = bs(l=5, cls=(aarch64_gpregz,), fname="rd") | |

| rn_n1 = bs(l=5, cls=(aarch64_gpreg_n1,), fname="rn") | |

| rm_n1 = bs(l=5, cls=(aarch64_gpreg_n1,), fname="rm") | |

| rn_na = bs(l=5, cls=(aarch64_gpreg_noarg,), fname="rn", order=-1) | |

| rn32_na = bs(l=5, cls=(aarch64_gpreg32_noarg,), fname="rn", order=-1) | |

| rn64_na = bs(l=5, cls=(aarch64_gpreg64_noarg,), fname="rn", order=-1) | |

| sd1 = bs(l=5, cls=(aarch64_simdreg_h,), fname="rt") | |

| sd2 = bs(l=5, cls=(aarch64_simdreg_h,), fname="rt2") | |

| sdn_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="rn") | |

| sdd_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="rd") | |

| sdm_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="rm") | |

| sda_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="ra") | |

| sdm_32_64_zero = bs(l=5, cls=(aarch64_simdreg_32_64_zero,), fname="rm") | |

| crn = bs(l=4, cls=(aarch64_crreg,), fname="crn") | |

| crm = bs(l=4, cls=(aarch64_crreg,), fname="crm") | |

| rn64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rn") | |

| rs64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rs") | |

| rm64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rm") | |

| rd64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rd") | |

| rt64 = bs(l=5, cls=(aarch64_gpregz64,), fname="rt") | |

| ra64 = bs(l=5, cls=(aarch64_gpregz64,), fname="ra") | |

| rn32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rn") | |

| rm32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rm") | |

| rd32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rd") | |

| rs32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rs") | |

| sd08 = bs(l=5, cls=(aarch64_simd08,), fname="rd") | |

| sd16 = bs(l=5, cls=(aarch64_simd16,), fname="rd") | |

| sd32 = bs(l=5, cls=(aarch64_simd32,), fname="rd") | |

| sd64 = bs(l=5, cls=(aarch64_simd64,), fname="rd") | |

| sd128 = bs(l=5, cls=(aarch64_simd128,), fname="rd") | |

| sn08 = bs(l=5, cls=(aarch64_simd08,), fname="rn") | |

| sn16 = bs(l=5, cls=(aarch64_simd16,), fname="rn") | |

| sn32 = bs(l=5, cls=(aarch64_simd32,), fname="rn") | |

| sn64 = bs(l=5, cls=(aarch64_simd64,), fname="rn") | |

| sn128 = bs(l=5, cls=(aarch64_simd128,), fname="rn") | |

| rt32 = bs(l=5, cls=(aarch64_gpregz32,), fname="rt") | |

| rt_isf = bs(l=5, cls=(aarch64_gpreg_isf,), fname="rt") | |

| rn64_deref = bs(l=5, cls=(aarch64_deref,), fname="rn") | |

| rn64_deref_sz = bs(l=5, cls=(aarch64_deref_size,), fname="rn") | |

| rn64_deref_sf = bs(l=5, cls=(aarch64_sf_scale,), fname="rn") | |

| rn64_deref_sd = bs(l=5, cls=(aarch64_sd_scale,), fname="rn") | |

| rn64_deref_nooff = bs(l=5, cls=(aarch64_deref_nooff,), fname="rn") | |

| imm_sft_12 = bs(l=12, cls=(aarch64_imm_sft,)) | |

| imm32_3 = bs(l=3, fname="imm") | |

| imm6 = bs(l=6, fname="imm", order=-1) | |

| imm3 = bs(l=3, fname="imm", order=-1) | |

| simm6 = bs(l=6, cls=(aarch64_int64_noarg, aarch64_arg), fname="imm", order=-1) | |

| simm9 = bs(l=9, cls=(aarch64_int64_noarg,), fname="imm", order=-1) | |

| simm7 = bs(l=7, cls=(aarch64_int64_noarg,), fname="imm", order=-1) | |

| nzcv = bs(l=4, cls=(aarch64_uint64_noarg, aarch64_arg), fname="nzcv", order=-1) | |

| uimm5 = bs(l=5, cls=(aarch64_uint64_noarg, aarch64_arg), fname="imm", order=-1) | |

| uimm12 = bs(l=12, cls=(aarch64_uint64_noarg,), fname="imm", order=-1) | |

| uimm16 = bs(l=16, cls=(aarch64_uint64_noarg, aarch64_arg), fname="imm", order=-1) | |

| uimm7 = bs(l=7, cls=(aarch64_uint64_noarg,), fname="imm", order=-1) | |

| uimm8 = bs(l=8, cls=(aarch64_uint64,), fname="imm", order=-1) | |

| op0 = bs(l=1, cls=(op0_value, aarch64_arg), fname="op0") | |

| op1 = bs(l=3, cls=(aarch64_uint64, aarch64_arg), fname="op1") | |

| op2 = bs(l=3, cls=(aarch64_uint64, aarch64_arg), fname="op2") | |

| imm16 = bs(l=16, fname="imm", order=-1) | |

| immlo = bs(l=2, fname='immlo') | |

| immhip = bs(l=19, cls=(aarch64_immhip_page,)) | |

| immhi = bs(l=19, cls=(aarch64_immhi_page,)) | |

| option = bs(l=3, fname='option', order=-1) | |

| rm_ext = bs(l=5, cls=(aarch64_gpreg_ext,), fname="rm") | |

| rm_sft = bs(l=5, cls=(aarch64_gpreg_sftimm,), fname="rm") | |

| rm_ext2 = bs(l=5, cls=(aarch64_gpreg_ext2,), fname="rm") | |

| rm_ext2_128 = bs(l=5, cls=(aarch64_gpreg_ext2_128,), fname="rm") | |

| imms = bs(l=6, cls=(aarch64_imm_nsr,), fname='imms') | |

| immr = bs(l=6, fname='immr') | |

| immn = bs(l=1, fname='immn') | |

| imm16_hw = bs(l=16, cls=(aarch64_imm_hw,), fname='imm') | |

| imm16_hw_sc = bs(l=16, cls=(aarch64_imm_hw_sc,), fname='imm') | |

| hw = bs(l=2, fname='hw') | |

| a_imms = bs(l=6, cls=(aarch64_imm_sf, aarch64_arg), fname="imm1", order=-1) | |

| a_immr = bs(l=6, cls=(aarch64_imm_sf, aarch64_arg), fname="imm1", order=-1) | |

| dictionary | adsu_name = {'ADD': 0, 'SUB': 1} |

| bs_adsu_name = bs_name(l=1, name=adsu_name) | |

| offs19 = bs(l=19, cls=(aarch64_offs,), fname='off') | |

| offs19pc = bs(l=19, cls=(aarch64_offs_pc,), fname='off') | |

| offs26 = bs(l=26, cls=(aarch64_offs,), fname='off') | |

| offs14 = bs(l=14, cls=(aarch64_offs,), fname='off') | |

| b40 = bs(l=5, cls=(aarch64_b40,), fname='b40', order=1) | |

| sdsize1 = bs(l=1, fname="size") | |

| sdsize = bs(l=2, fname="size") | |

| opsize = bs(l=2, fname="size") | |

| sd = bs(l=5, cls=(aarch64_simdreg,), fname='sd') | |

| opc = bs(l=1, fname='opc', order=-1) | |

| alias | |

| dictionary | logic_name = {'AND': 0, 'ORR': 1, 'EOR': 2} |

| bs_logic_name = bs_name(l=2, name=logic_name) | |

| dictionary | logicbf_name = {'SBFM': 0b00, 'BFM': 0b01, 'UBFM': 0b10} |

| bs_logicbf_name = bs_name(l=2, name=logicbf_name) | |

| bcond | |

| cond_arg = bs(l=4, cls=(aarch64_cond_arg,), fname="cond") | |

| cond_inv_arg = bs(l=4, cls=(aarch64_cond_inv_arg,), fname="cond") | |

| post_pre = bs(l=1, order=-1, fname='postpre') | |

| dictionary | ccmp_name = {'CCMN': 0, 'CCMP': 1} |

| bs_ccmp_name = bs_name(l=1, name=ccmp_name) | |

| dictionary | ldst_b_name = {'STRB': 0, 'LDRB': 1} |

| bs_ldst_b_name = bs_name(l=1, name=ldst_b_name) | |

| dictionary | ldst_name = {'STR': 0, 'LDR': 1} |

| bs_ldst_name = bs_name(l=1, name=ldst_name) | |

| dictionary | ldst_h_name = {'STRH': 0, 'LDRH': 1} |

| bs_ldst_h_name = bs_name(l=1, name=ldst_h_name) | |

| dictionary | ldst_tb_name = {'STTRB': 0, 'LDTRB': 1} |

| bs_ldst_tb_name = bs_name(l=1, name=ldst_tb_name) | |

| dictionary | ldst_th_name = {'STTRH': 0, 'LDTRH': 1} |

| bs_ldst_th_name = bs_name(l=1, name=ldst_th_name) | |

| dictionary | ldst_ub_name = {'STURB': 0, 'LDURB': 1} |

| bs_ldst_ub_name = bs_name(l=1, name=ldst_ub_name) | |

| dictionary | ldst_u_name = {'STUR': 0, 'LDUR': 1} |

| bs_ldst_u_name = bs_name(l=1, name=ldst_u_name) | |

| dictionary | ldst_t_name = {'STTR': 0, 'LDTR': 1} |

| bs_ldst_st_name = bs_name(l=1, name=ldst_t_name) | |

| dictionary | ldst_1u_name = {'STUR': 0b0, 'LDUR': 0b1} |

| bs_ldst_1u_name = bs_name(l=1, name=ldst_1u_name) | |

| dictionary | ldst_uh_name = {'STURH': 0, 'LDURH': 1} |

| bs_ldst_uh_name = bs_name(l=1, name=ldst_uh_name) | |

| dictionary | ldst_sw_name = {'STRSW': 0, 'LDRSW': 1} |

| bs_ldst_sw_name = bs_name(l=1, name=ldst_sw_name) | |

| dictionary | movwide_name = {'MOVN': 0b00, 'MOVZ': 0b10} |

| bs_movwide_name = bs_name(l=2, name=movwide_name) | |

| dictionary | ldstp_name = {'STP': 0b0, 'LDP': 0b1} |

| bs_ldstp_name = bs_name(l=1, name=ldstp_name) | |

| dictionary | datap0_name |

| bs_datap0_name = bs_name(l=6, name=datap0_name) | |

| dictionary | datap1_name |

| bs_datap1_name = bs_name(l=6, name=datap1_name) | |

| swapargs = bs_swapargs(l=1, fname="swap", mn_mod=list(range(1 << 1))) | |

| dictionary | shiftr_name = {'LSL': 0b00, 'LSR': 0b01, 'ASR': 0b10, 'ROR': 0b11} |

| bs_shiftr_name = bs_name(l=2, name=shiftr_name) | |

| dictionary | msr_name = {'MSR': 0b0, 'MRS': 0b1} |

| bs_msr_name = bs_name(l=1, name=msr_name) | |

| stacctype = bs_mod_name(l=1, fname='order', mn_mod=['', 'L']) | |

| ltacctype = bs_mod_name(l=1, fname='order', mn_mod=['', 'A']) | |

| def miasm.arch.aarch64.arch.aarch64op | ( | name, | |

| fields, | |||

args = None, |

|||

alias = False |

|||

| ) |

| def miasm.arch.aarch64.arch.cb_deref_ext2op | ( | t | ) |

| def miasm.arch.aarch64.arch.cb_deref_nooff | ( | t | ) |

| def miasm.arch.aarch64.arch.cb_deref_pc_nooff | ( | tokens | ) |

| def miasm.arch.aarch64.arch.cb_deref_pc_off | ( | tokens | ) |

| def miasm.arch.aarch64.arch.cb_deref_post | ( | t | ) |

| def miasm.arch.aarch64.arch.cb_deref_pre | ( | t | ) |

| def miasm.arch.aarch64.arch.cb_deref_pre_wb | ( | t | ) |

| def miasm.arch.aarch64.arch.cb_extend | ( | tokens | ) |

| def miasm.arch.aarch64.arch.cb_extreg | ( | tokens | ) |

| def miasm.arch.aarch64.arch.cb_shift | ( | tokens | ) |

| def miasm.arch.aarch64.arch.cb_shift_sc | ( | tokens | ) |

| def miasm.arch.aarch64.arch.cb_shiftreg | ( | tokens | ) |

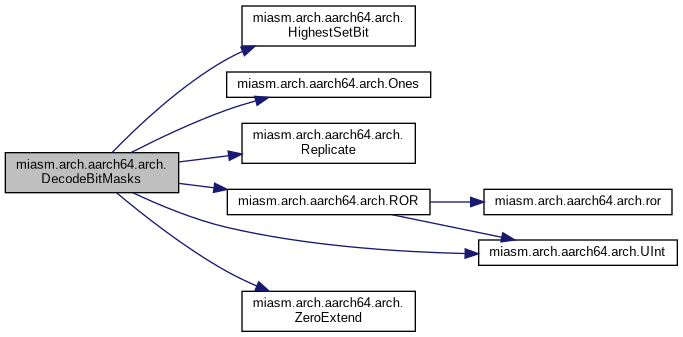

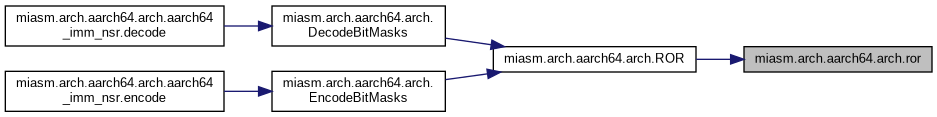

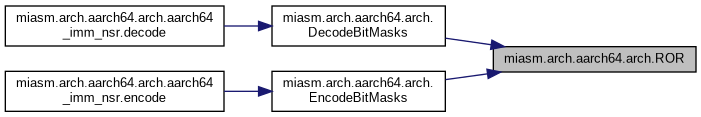

| def miasm.arch.aarch64.arch.DecodeBitMasks | ( | M, | |

| immN, | |||

| imms, | |||

| immr, | |||

| immediate | |||

| ) |

@M: 32 or 64 @immN: 1-bit @imms: 6-bit @immr: 6-bit @immediate: boolean

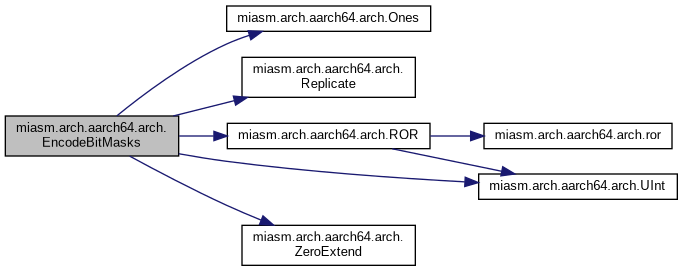

| def miasm.arch.aarch64.arch.EncodeBitMasks | ( | wmask | ) |

| def miasm.arch.aarch64.arch.get_size | ( | parent | ) |

| def miasm.arch.aarch64.arch.HighestSetBit | ( | x | ) |

| def miasm.arch.aarch64.arch.Ones | ( | N | ) |

| def miasm.arch.aarch64.arch.Replicate | ( | x, | |

| N | |||

| ) |

| def miasm.arch.aarch64.arch.rol | ( | value, | |

| amount, | |||

| size | |||

| ) |

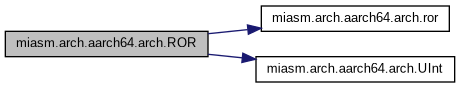

| def miasm.arch.aarch64.arch.ror | ( | value, | |

| amount, | |||

| size | |||

| ) |

| def miasm.arch.aarch64.arch.ROR | ( | x, | |

| shift | |||

| ) |

| def miasm.arch.aarch64.arch.set_imm_to_size | ( | size, | |

| expr | |||

| ) |

| def miasm.arch.aarch64.arch.set_mem_off | ( | parent, | |

| imm | |||

| ) |

| def miasm.arch.aarch64.arch.test_set_sf | ( | parent, | |

| size | |||

| ) |

| def miasm.arch.aarch64.arch.UInt | ( | x | ) |

| def miasm.arch.aarch64.arch.ZeroExtend | ( | x, | |

| N | |||

| ) |

| miasm.arch.aarch64.arch.a_immr = bs(l=6, cls=(aarch64_imm_sf, aarch64_arg), fname="imm1", order=-1) |

| miasm.arch.aarch64.arch.a_imms = bs(l=6, cls=(aarch64_imm_sf, aarch64_arg), fname="imm1", order=-1) |

| dictionary miasm.arch.aarch64.arch.adsu_name = {'ADD': 0, 'SUB': 1} |

| miasm.arch.aarch64.arch.alias |

| miasm.arch.aarch64.arch.all_binaryop_shiftleft_t = literal_list(["LSL"]).setParseAction(cb_shift) |

| miasm.arch.aarch64.arch.all_extend2_t = literal_list(extend2_lst).setParseAction(cb_extreg) |

| miasm.arch.aarch64.arch.all_extend_t = literal_list(extend_lst).setParseAction(cb_extreg) |

| miasm.arch.aarch64.arch.b40 = bs(l=5, cls=(aarch64_b40,), fname='b40', order=1) |

| miasm.arch.aarch64.arch.bcond |

| list miasm.arch.aarch64.arch.BRCOND = ['B.' + cond for cond in CONDS] + ['CBZ', 'CBNZ', 'TBZ', 'TBNZ'] |

| miasm.arch.aarch64.arch.bs_datap0_name = bs_name(l=6, name=datap0_name) |

| miasm.arch.aarch64.arch.bs_datap1_name = bs_name(l=6, name=datap1_name) |

| miasm.arch.aarch64.arch.bs_ldst_1u_name = bs_name(l=1, name=ldst_1u_name) |

| miasm.arch.aarch64.arch.bs_ldst_b_name = bs_name(l=1, name=ldst_b_name) |

| miasm.arch.aarch64.arch.bs_ldst_h_name = bs_name(l=1, name=ldst_h_name) |

| miasm.arch.aarch64.arch.bs_ldst_st_name = bs_name(l=1, name=ldst_t_name) |

| miasm.arch.aarch64.arch.bs_ldst_sw_name = bs_name(l=1, name=ldst_sw_name) |

| miasm.arch.aarch64.arch.bs_ldst_tb_name = bs_name(l=1, name=ldst_tb_name) |

| miasm.arch.aarch64.arch.bs_ldst_th_name = bs_name(l=1, name=ldst_th_name) |

| miasm.arch.aarch64.arch.bs_ldst_u_name = bs_name(l=1, name=ldst_u_name) |

| miasm.arch.aarch64.arch.bs_ldst_ub_name = bs_name(l=1, name=ldst_ub_name) |

| miasm.arch.aarch64.arch.bs_ldst_uh_name = bs_name(l=1, name=ldst_uh_name) |

| miasm.arch.aarch64.arch.bs_ldstp_name = bs_name(l=1, name=ldstp_name) |

| miasm.arch.aarch64.arch.bs_logic_name = bs_name(l=2, name=logic_name) |

| miasm.arch.aarch64.arch.bs_logicbf_name = bs_name(l=2, name=logicbf_name) |

| miasm.arch.aarch64.arch.bs_movwide_name = bs_name(l=2, name=movwide_name) |

| miasm.arch.aarch64.arch.bs_shiftr_name = bs_name(l=2, name=shiftr_name) |

| dictionary miasm.arch.aarch64.arch.ccmp_name = {'CCMN': 0, 'CCMP': 1} |

| miasm.arch.aarch64.arch.COMMA = Suppress(",") |

| miasm.arch.aarch64.arch.cond_arg = bs(l=4, cls=(aarch64_cond_arg,), fname="cond") |

| miasm.arch.aarch64.arch.cond_inv_arg = bs(l=4, cls=(aarch64_cond_inv_arg,), fname="cond") |

| list miasm.arch.aarch64.arch.CONDS |

| miasm.arch.aarch64.arch.conds_expr |

| miasm.arch.aarch64.arch.conds_info |

| list miasm.arch.aarch64.arch.CONDS_INV |

| miasm.arch.aarch64.arch.conds_inv_expr |

| miasm.arch.aarch64.arch.conds_inv_info |

| miasm.arch.aarch64.arch.console_handler = logging.StreamHandler() |

| miasm.arch.aarch64.arch.crm = bs(l=4, cls=(aarch64_crreg,), fname="crm") |

| miasm.arch.aarch64.arch.crn = bs(l=4, cls=(aarch64_crreg,), fname="crn") |

| dictionary miasm.arch.aarch64.arch.datap0_name |

| dictionary miasm.arch.aarch64.arch.datap1_name |

| tuple miasm.arch.aarch64.arch.deref = (deref_off_post | deref_off_pre_wb | deref_off_pre | deref_nooff) |

| tuple miasm.arch.aarch64.arch.deref_ext2 = (LBRACK + gpregs_32_64 + COMMA + gpregs_32_64 + Optional(all_extend2_t + base_expr) + RBRACK).setParseAction(cb_deref_ext2op) |

| tuple miasm.arch.aarch64.arch.deref_nooff = (LBRACK + gpregs64_info.parser + RBRACK).setParseAction(cb_deref_nooff) |

| tuple miasm.arch.aarch64.arch.deref_off_post = (LBRACK + gpregs64_info.parser + RBRACK + COMMA + base_expr).setParseAction(cb_deref_post) |

| tuple miasm.arch.aarch64.arch.deref_off_pre = (LBRACK + gpregs64_info.parser + COMMA + base_expr + RBRACK).setParseAction(cb_deref_pre) |

| tuple miasm.arch.aarch64.arch.deref_off_pre_wb = (LBRACK + gpregs64_info.parser + COMMA + base_expr + RBRACK + POSTINC).setParseAction(cb_deref_pre_wb) |

| tuple miasm.arch.aarch64.arch.deref_pc = (deref_pc_off | deref_pc_nooff) |

| tuple miasm.arch.aarch64.arch.deref_pc_nooff = (LBRACK + Literal("PC") + RBRACK).setParseAction(cb_deref_pc_nooff) |

| tuple miasm.arch.aarch64.arch.deref_pc_off = (LBRACK + Literal("PC") + COMMA + base_expr + RBRACK).setParseAction(cb_deref_pc_off) |

| dictionary miasm.arch.aarch64.arch.EXT2_OP |

| miasm.arch.aarch64.arch.EXT2_OP_INV = dict((value, key) for key, value in viewitems(EXT2_OP)) |

| list miasm.arch.aarch64.arch.extend2_lst = ['UXTW', 'LSL', 'SXTW', 'SXTX'] |

| list miasm.arch.aarch64.arch.extend_lst = ['UXTB', 'UXTH', 'UXTW', 'UXTX', 'SXTB', 'SXTH', 'SXTW', 'SXTX'] |

| tuple miasm.arch.aarch64.arch.gpregs_32_64 = (gpregs32_info.parser | gpregs64_info.parser) |

| dictionary miasm.arch.aarch64.arch.gpregs_info |

| tuple miasm.arch.aarch64.arch.gpregsz_32_64 = (gpregsz32_info.parser | gpregsz64_info.parser | base_expr) |

| dictionary miasm.arch.aarch64.arch.gpregsz_info |

| tuple miasm.arch.aarch64.arch.gpregz32_extend = (gpregsz32_info.parser + Optional(all_extend_t + base_expr)).setParseAction(cb_extend) |

| tuple miasm.arch.aarch64.arch.gpregz64_extend = (gpregsz64_info.parser + Optional(all_extend_t + base_expr)).setParseAction(cb_extend) |

| miasm.arch.aarch64.arch.hw = bs(l=2, fname='hw') |

| miasm.arch.aarch64.arch.imm16 = bs(l=16, fname="imm", order=-1) |

| miasm.arch.aarch64.arch.imm16_hw = bs(l=16, cls=(aarch64_imm_hw,), fname='imm') |

| miasm.arch.aarch64.arch.imm16_hw_sc = bs(l=16, cls=(aarch64_imm_hw_sc,), fname='imm') |

| miasm.arch.aarch64.arch.imm3 = bs(l=3, fname="imm", order=-1) |

| miasm.arch.aarch64.arch.imm32_3 = bs(l=3, fname="imm") |

| miasm.arch.aarch64.arch.imm6 = bs(l=6, fname="imm", order=-1) |

| miasm.arch.aarch64.arch.imm_sft_12 = bs(l=12, cls=(aarch64_imm_sft,)) |

| miasm.arch.aarch64.arch.immhi = bs(l=19, cls=(aarch64_immhi_page,)) |

| miasm.arch.aarch64.arch.immhip = bs(l=19, cls=(aarch64_immhip_page,)) |

| miasm.arch.aarch64.arch.immlo = bs(l=2, fname='immlo') |

| miasm.arch.aarch64.arch.immn = bs(l=1, fname='immn') |

| miasm.arch.aarch64.arch.immr = bs(l=6, fname='immr') |

| miasm.arch.aarch64.arch.imms = bs(l=6, cls=(aarch64_imm_nsr,), fname='imms') |

| miasm.arch.aarch64.arch.LBRACK = Suppress("[") |

| dictionary miasm.arch.aarch64.arch.ldst_1u_name = {'STUR': 0b0, 'LDUR': 0b1} |

| dictionary miasm.arch.aarch64.arch.ldst_b_name = {'STRB': 0, 'LDRB': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_h_name = {'STRH': 0, 'LDRH': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_name = {'STR': 0, 'LDR': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_sw_name = {'STRSW': 0, 'LDRSW': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_t_name = {'STTR': 0, 'LDTR': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_tb_name = {'STTRB': 0, 'LDTRB': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_th_name = {'STTRH': 0, 'LDTRH': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_u_name = {'STUR': 0, 'LDUR': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_ub_name = {'STURB': 0, 'LDURB': 1} |

| dictionary miasm.arch.aarch64.arch.ldst_uh_name = {'STURH': 0, 'LDURH': 1} |

| dictionary miasm.arch.aarch64.arch.ldstp_name = {'STP': 0b0, 'LDP': 0b1} |

| miasm.arch.aarch64.arch.log = logging.getLogger("aarch64dis") |

| dictionary miasm.arch.aarch64.arch.logic_name = {'AND': 0, 'ORR': 1, 'EOR': 2} |

| dictionary miasm.arch.aarch64.arch.logicbf_name = {'SBFM': 0b00, 'BFM': 0b01, 'UBFM': 0b10} |

| miasm.arch.aarch64.arch.ltacctype = bs_mod_name(l=1, fname='order', mn_mod=['', 'A']) |

| miasm.arch.aarch64.arch.modf = bs_mod_name(l=1, fname='modf', mn_mod=['', 'S']) |

| dictionary miasm.arch.aarch64.arch.movwide_name = {'MOVN': 0b00, 'MOVZ': 0b10} |

| dictionary miasm.arch.aarch64.arch.msr_name = {'MSR': 0b0, 'MRS': 0b1} |

| miasm.arch.aarch64.arch.nzcv = bs(l=4, cls=(aarch64_uint64_noarg, aarch64_arg), fname="nzcv", order=-1) |

| miasm.arch.aarch64.arch.offs14 = bs(l=14, cls=(aarch64_offs,), fname='off') |

| miasm.arch.aarch64.arch.offs19 = bs(l=19, cls=(aarch64_offs,), fname='off') |

| miasm.arch.aarch64.arch.offs19pc = bs(l=19, cls=(aarch64_offs_pc,), fname='off') |

| miasm.arch.aarch64.arch.offs26 = bs(l=26, cls=(aarch64_offs,), fname='off') |

| miasm.arch.aarch64.arch.op0 = bs(l=1, cls=(op0_value, aarch64_arg), fname="op0") |

| miasm.arch.aarch64.arch.op1 = bs(l=3, cls=(aarch64_uint64, aarch64_arg), fname="op1") |

| miasm.arch.aarch64.arch.op2 = bs(l=3, cls=(aarch64_uint64, aarch64_arg), fname="op2") |

| miasm.arch.aarch64.arch.opc = bs(l=1, fname='opc', order=-1) |

| miasm.arch.aarch64.arch.opsize = bs(l=2, fname="size") |

| miasm.arch.aarch64.arch.option = bs(l=3, fname='option', order=-1) |

| miasm.arch.aarch64.arch.post_pre = bs(l=1, order=-1, fname='postpre') |

| miasm.arch.aarch64.arch.POSTINC = Suppress("!") |

| miasm.arch.aarch64.arch.ra = bs(l=5, cls=(aarch64_gpregz,), fname="ra") |

| miasm.arch.aarch64.arch.ra64 = bs(l=5, cls=(aarch64_gpregz64,), fname="ra") |

| miasm.arch.aarch64.arch.RBRACK = Suppress("]") |

| miasm.arch.aarch64.arch.rd = bs(l=5, cls=(aarch64_gpreg,), fname="rd") |

| miasm.arch.aarch64.arch.rd32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rd") |

| miasm.arch.aarch64.arch.rd64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rd") |

| miasm.arch.aarch64.arch.rdz = bs(l=5, cls=(aarch64_gpregz,), fname="rd") |

| tuple miasm.arch.aarch64.arch.reg_ext_off = (gpregz32_extend | gpregz64_extend) |

| dictionary miasm.arch.aarch64.arch.replace_regs |

| miasm.arch.aarch64.arch.rm = bs(l=5, cls=(aarch64_gpreg,), fname="rm") |

| miasm.arch.aarch64.arch.rm32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rm") |

| miasm.arch.aarch64.arch.rm64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rm") |

| miasm.arch.aarch64.arch.rm_ext = bs(l=5, cls=(aarch64_gpreg_ext,), fname="rm") |

| miasm.arch.aarch64.arch.rm_ext2 = bs(l=5, cls=(aarch64_gpreg_ext2,), fname="rm") |

| miasm.arch.aarch64.arch.rm_ext2_128 = bs(l=5, cls=(aarch64_gpreg_ext2_128,), fname="rm") |

| miasm.arch.aarch64.arch.rm_n1 = bs(l=5, cls=(aarch64_gpreg_n1,), fname="rm") |

| miasm.arch.aarch64.arch.rm_sft = bs(l=5, cls=(aarch64_gpreg_sftimm,), fname="rm") |

| miasm.arch.aarch64.arch.rmz = bs(l=5, cls=(aarch64_gpregz,), fname="rm") |

| miasm.arch.aarch64.arch.rn = bs(l=5, cls=(aarch64_gpreg,), fname="rn") |

| miasm.arch.aarch64.arch.rn0 = bs(l=5, cls=(aarch64_gpreg0,), fname="rn") |

| miasm.arch.aarch64.arch.rn32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rn") |

| miasm.arch.aarch64.arch.rn32_na = bs(l=5, cls=(aarch64_gpreg32_noarg,), fname="rn", order=-1) |

| miasm.arch.aarch64.arch.rn64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rn") |

| miasm.arch.aarch64.arch.rn64_deref = bs(l=5, cls=(aarch64_deref,), fname="rn") |

| miasm.arch.aarch64.arch.rn64_deref_nooff = bs(l=5, cls=(aarch64_deref_nooff,), fname="rn") |

| miasm.arch.aarch64.arch.rn64_deref_sd = bs(l=5, cls=(aarch64_sd_scale,), fname="rn") |

| miasm.arch.aarch64.arch.rn64_deref_sf = bs(l=5, cls=(aarch64_sf_scale,), fname="rn") |

| miasm.arch.aarch64.arch.rn64_deref_sz = bs(l=5, cls=(aarch64_deref_size,), fname="rn") |

| miasm.arch.aarch64.arch.rn64_na = bs(l=5, cls=(aarch64_gpreg64_noarg,), fname="rn", order=-1) |

| miasm.arch.aarch64.arch.rn64_v = bs(l=5, cls=(aarch64_gpreg64_nodec,), fname='rn', order=-1) |

| miasm.arch.aarch64.arch.rn_n1 = bs(l=5, cls=(aarch64_gpreg_n1,), fname="rn") |

| miasm.arch.aarch64.arch.rn_na = bs(l=5, cls=(aarch64_gpreg_noarg,), fname="rn", order=-1) |

| miasm.arch.aarch64.arch.rnz = bs(l=5, cls=(aarch64_gpregz,), fname="rn") |

| miasm.arch.aarch64.arch.rs = bs(l=5, cls=(aarch64_gpreg,), fname="rs") |

| miasm.arch.aarch64.arch.rs32 = bs(l=5, cls=(aarch64_gpreg32,), fname="rs") |

| miasm.arch.aarch64.arch.rs64 = bs(l=5, cls=(aarch64_gpreg64,), fname="rs") |

| miasm.arch.aarch64.arch.rt = bs(l=5, cls=(aarch64_gpregz,), fname="rt") |

| miasm.arch.aarch64.arch.rt2 = bs(l=5, cls=(aarch64_gpregz,), fname="rt2") |

| miasm.arch.aarch64.arch.rt32 = bs(l=5, cls=(aarch64_gpregz32,), fname="rt") |

| miasm.arch.aarch64.arch.rt64 = bs(l=5, cls=(aarch64_gpregz64,), fname="rt") |

| miasm.arch.aarch64.arch.rt_isf = bs(l=5, cls=(aarch64_gpreg_isf,), fname="rt") |

| miasm.arch.aarch64.arch.sd = bs(l=5, cls=(aarch64_simdreg,), fname='sd') |

| miasm.arch.aarch64.arch.sd08 = bs(l=5, cls=(aarch64_simd08,), fname="rd") |

| miasm.arch.aarch64.arch.sd1 = bs(l=5, cls=(aarch64_simdreg_h,), fname="rt") |

| miasm.arch.aarch64.arch.sd128 = bs(l=5, cls=(aarch64_simd128,), fname="rd") |

| miasm.arch.aarch64.arch.sd16 = bs(l=5, cls=(aarch64_simd16,), fname="rd") |

| miasm.arch.aarch64.arch.sd2 = bs(l=5, cls=(aarch64_simdreg_h,), fname="rt2") |

| miasm.arch.aarch64.arch.sd32 = bs(l=5, cls=(aarch64_simd32,), fname="rd") |

| miasm.arch.aarch64.arch.sd64 = bs(l=5, cls=(aarch64_simd64,), fname="rd") |

| miasm.arch.aarch64.arch.sda_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="ra") |

| miasm.arch.aarch64.arch.sdd_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="rd") |

| miasm.arch.aarch64.arch.sdm_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="rm") |

| miasm.arch.aarch64.arch.sdm_32_64_zero = bs(l=5, cls=(aarch64_simdreg_32_64_zero,), fname="rm") |

| miasm.arch.aarch64.arch.sdn_32_64 = bs(l=5, cls=(aarch64_simdreg_32_64,), fname="rn") |

| miasm.arch.aarch64.arch.sdsize = bs(l=2, fname="size") |

| miasm.arch.aarch64.arch.sdsize1 = bs(l=1, fname="size") |

| miasm.arch.aarch64.arch.sf = bs(l=1, fname='sf', order=-1) |

| miasm.arch.aarch64.arch.shift = bs(l=2, fname='shift') |

| dictionary miasm.arch.aarch64.arch.shift2expr_dct = {'LSL': '<<', 'LSR': '>>', 'ASR': 'a>>', 'ROR': '>>>'} |

| tuple miasm.arch.aarch64.arch.shift32_off = (gpregsz32_info.parser + Optional(all_binaryop_lsl_t + base_expr)).setParseAction(cb_shiftreg) |

| tuple miasm.arch.aarch64.arch.shift64_off = (gpregsz64_info.parser + Optional(all_binaryop_lsl_t + base_expr)).setParseAction(cb_shiftreg) |

| list miasm.arch.aarch64.arch.shift_expr = ["<<", ">>", "a>>", '>>>'] |

| tuple miasm.arch.aarch64.arch.shift_off = (shift32_off | shift64_off) |

| list miasm.arch.aarch64.arch.shift_str = ["LSL", "LSR", "ASR", "ROR"] |

| tuple miasm.arch.aarch64.arch.shiftimm_imm_sc = (base_expr + all_binaryop_shiftleft_t + base_expr).setParseAction(cb_shift_sc) |

| tuple miasm.arch.aarch64.arch.shiftimm_off_sc = shiftimm_imm_sc | base_expr |

| dictionary miasm.arch.aarch64.arch.shiftr_name = {'LSL': 0b00, 'LSR': 0b01, 'ASR': 0b10, 'ROR': 0b11} |

| tuple miasm.arch.aarch64.arch.simdregs = (simd08_info.parser | simd16_info.parser | simd32_info.parser | simd64_info.parser) |

| tuple miasm.arch.aarch64.arch.simdregs_h = (simd32_info.parser | simd64_info.parser | simd128_info.parser) |

| tuple miasm.arch.aarch64.arch.simdregs_h_zero = (simd32_info.parser | simd64_info.parser | simd128_info.parser | base_expr) |

| dictionary miasm.arch.aarch64.arch.simds_info |

| miasm.arch.aarch64.arch.simm6 = bs(l=6, cls=(aarch64_int64_noarg, aarch64_arg), fname="imm", order=-1) |

| miasm.arch.aarch64.arch.simm7 = bs(l=7, cls=(aarch64_int64_noarg,), fname="imm", order=-1) |

| miasm.arch.aarch64.arch.simm9 = bs(l=9, cls=(aarch64_int64_noarg,), fname="imm", order=-1) |

| miasm.arch.aarch64.arch.sn08 = bs(l=5, cls=(aarch64_simd08,), fname="rn") |

| miasm.arch.aarch64.arch.sn128 = bs(l=5, cls=(aarch64_simd128,), fname="rn") |

| miasm.arch.aarch64.arch.sn16 = bs(l=5, cls=(aarch64_simd16,), fname="rn") |

| miasm.arch.aarch64.arch.sn32 = bs(l=5, cls=(aarch64_simd32,), fname="rn") |

| miasm.arch.aarch64.arch.sn64 = bs(l=5, cls=(aarch64_simd64,), fname="rn") |

| miasm.arch.aarch64.arch.stacctype = bs_mod_name(l=1, fname='order', mn_mod=['', 'L']) |

| miasm.arch.aarch64.arch.swapargs = bs_swapargs(l=1, fname="swap", mn_mod=list(range(1 << 1))) |

| miasm.arch.aarch64.arch.uimm12 = bs(l=12, cls=(aarch64_uint64_noarg,), fname="imm", order=-1) |

| miasm.arch.aarch64.arch.uimm16 = bs(l=16, cls=(aarch64_uint64_noarg, aarch64_arg), fname="imm", order=-1) |

| miasm.arch.aarch64.arch.uimm5 = bs(l=5, cls=(aarch64_uint64_noarg, aarch64_arg), fname="imm", order=-1) |

| miasm.arch.aarch64.arch.uimm7 = bs(l=7, cls=(aarch64_uint64_noarg,), fname="imm", order=-1) |

| miasm.arch.aarch64.arch.uimm8 = bs(l=8, cls=(aarch64_uint64,), fname="imm", order=-1) |