|

miasm

Reverse engineering framework

|

|

miasm

Reverse engineering framework

|

Classes | |

| class | aarch64info |

| class | ir_aarch64b |

| class | ir_aarch64l |

Functions | |

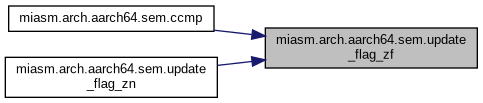

| def | update_flag_zf (a) |

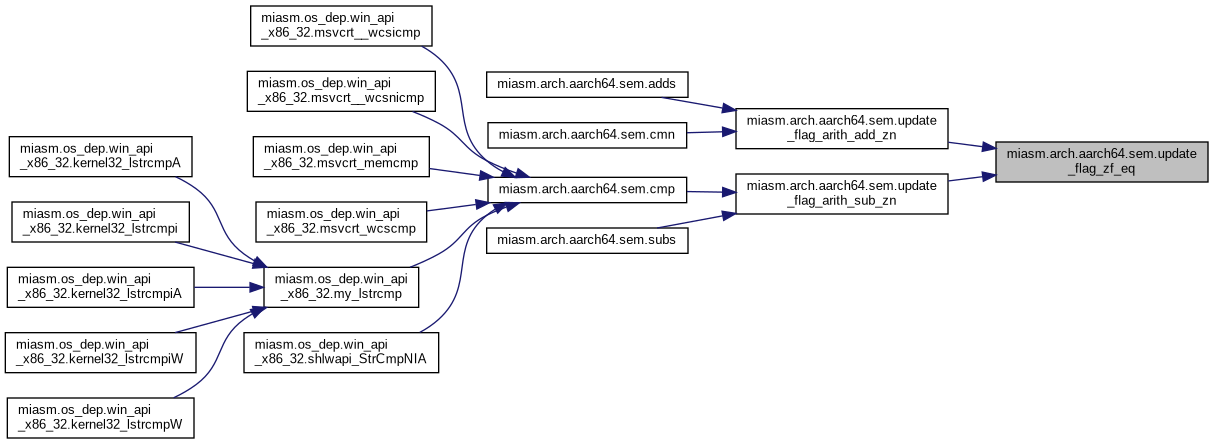

| def | update_flag_zf_eq (a, b) |

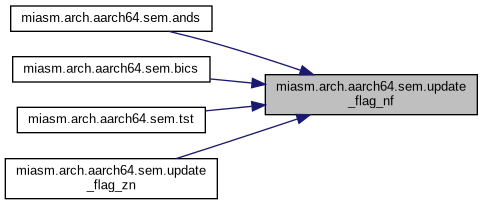

| def | update_flag_nf (arg) |

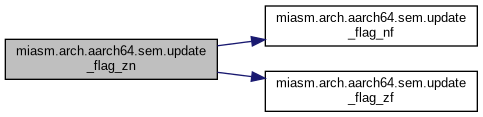

| def | update_flag_zn (a) |

| def | check_ops_msb (a, b, c) |

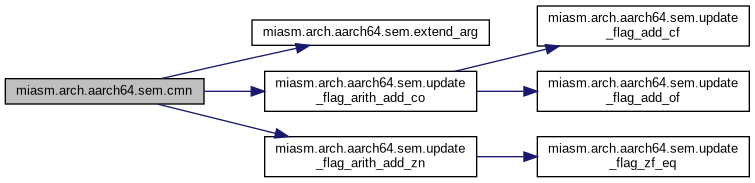

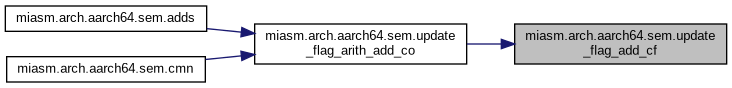

| def | update_flag_add_cf (op1, op2) |

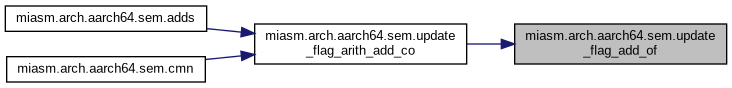

| def | update_flag_add_of (op1, op2) |

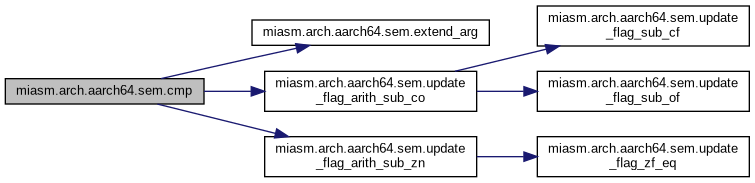

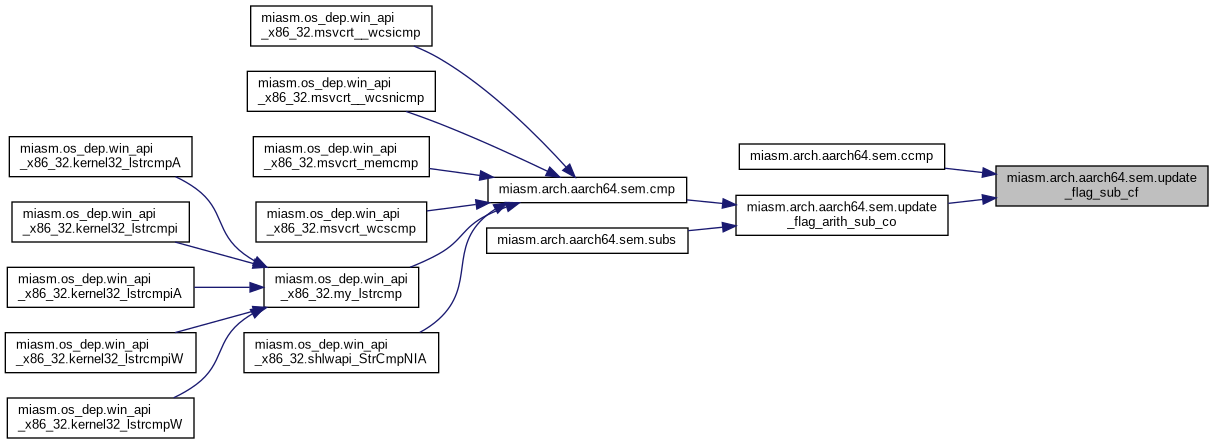

| def | update_flag_sub_cf (op1, op2) |

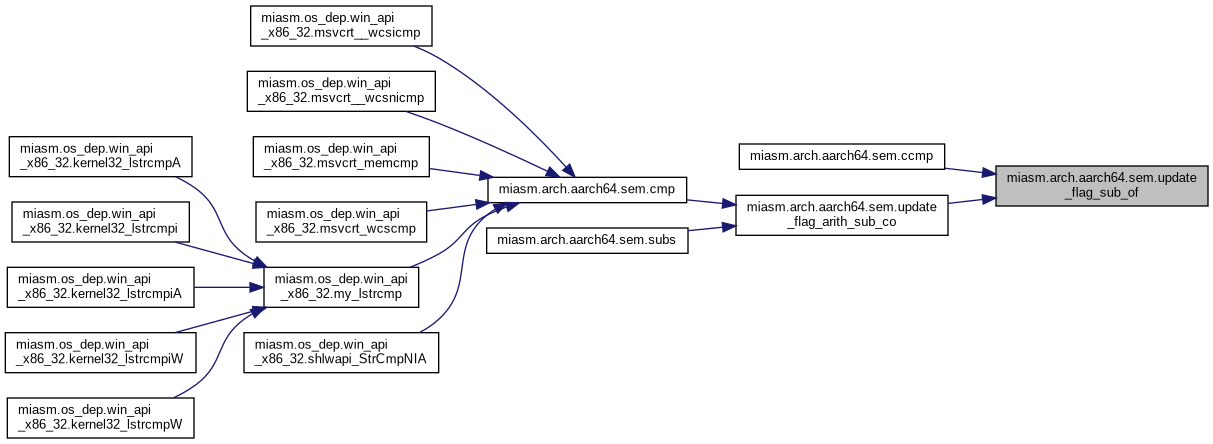

| def | update_flag_sub_of (op1, op2) |

| def | update_flag_arith_add_co (arg1, arg2) |

| def | update_flag_arith_add_zn (arg1, arg2) |

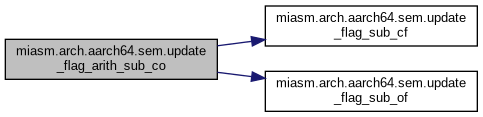

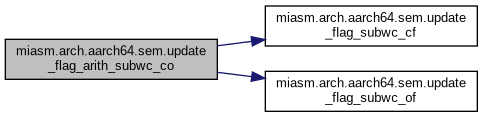

| def | update_flag_arith_sub_co (arg1, arg2) |

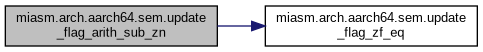

| def | update_flag_arith_sub_zn (arg1, arg2) |

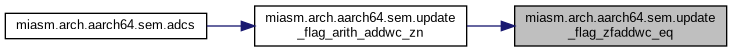

| def | update_flag_zfaddwc_eq (arg1, arg2, arg3) |

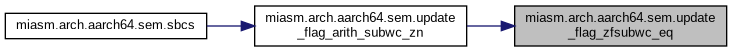

| def | update_flag_zfsubwc_eq (arg1, arg2, arg3) |

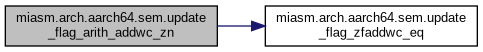

| def | update_flag_arith_addwc_zn (arg1, arg2, arg3) |

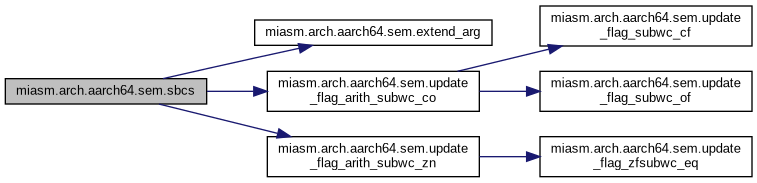

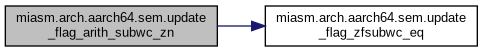

| def | update_flag_arith_subwc_zn (arg1, arg2, arg3) |

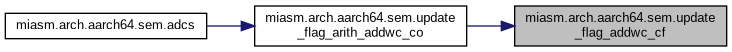

| def | update_flag_addwc_cf (op1, op2, op3) |

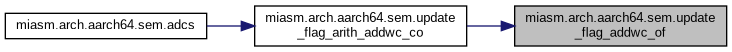

| def | update_flag_addwc_of (op1, op2, op3) |

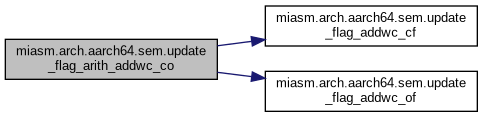

| def | update_flag_arith_addwc_co (arg1, arg2, arg3) |

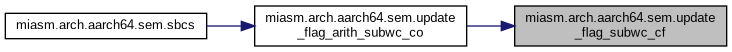

| def | update_flag_subwc_cf (op1, op2, op3) |

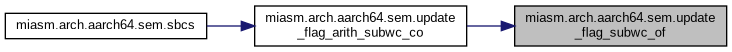

| def | update_flag_subwc_of (op1, op2, op3) |

| def | update_flag_arith_subwc_co (arg1, arg2, arg3) |

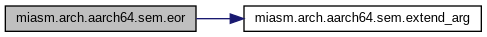

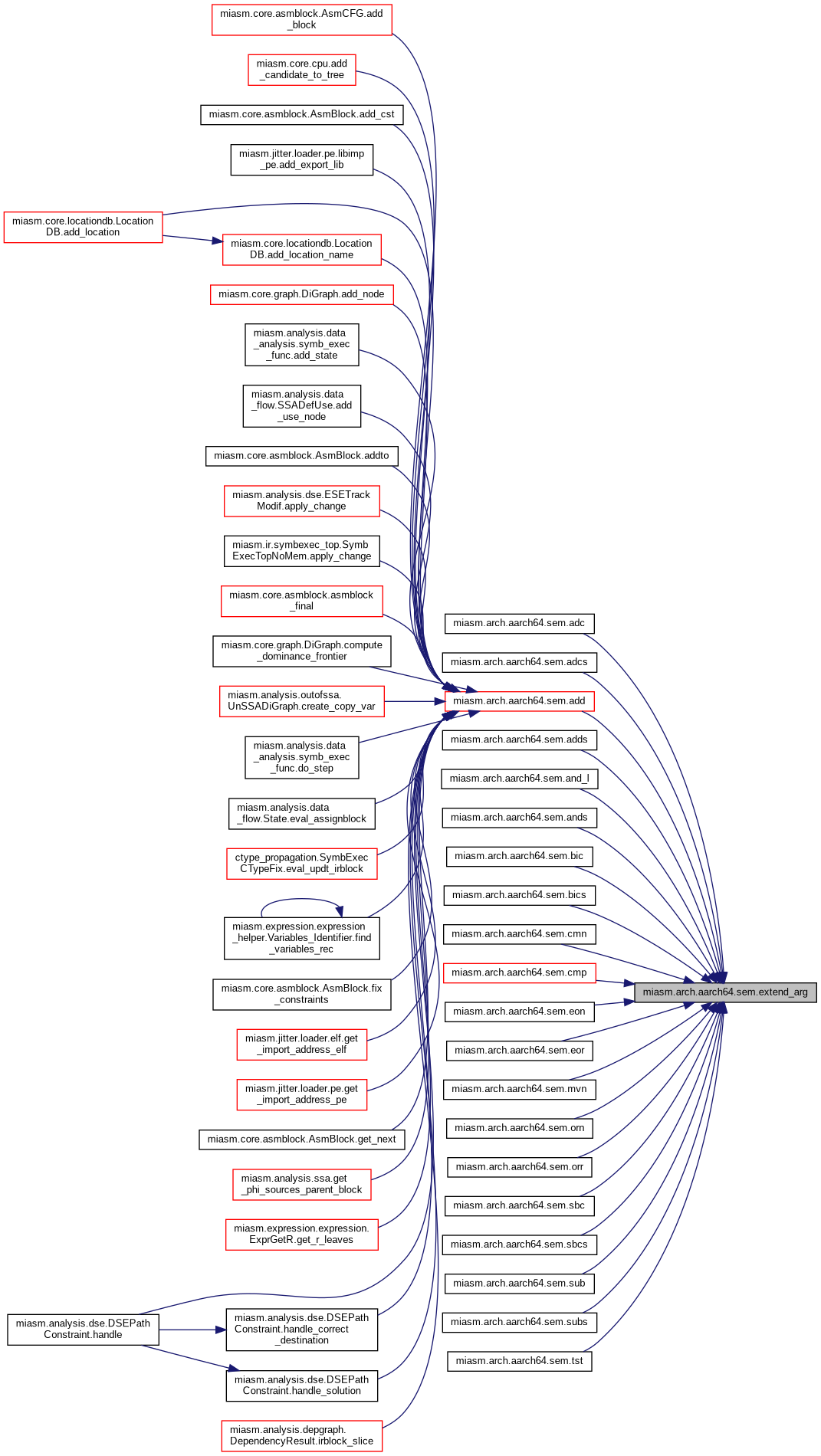

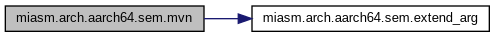

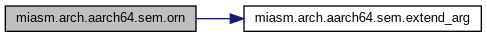

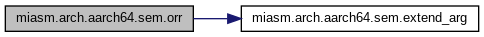

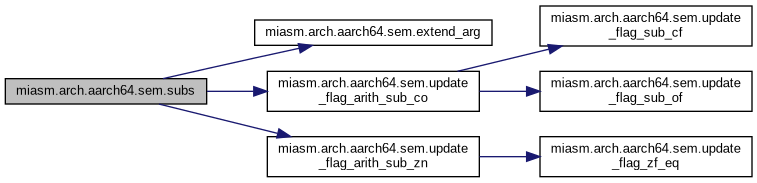

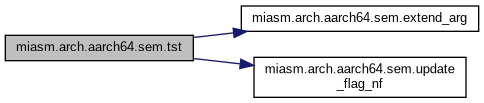

| def | extend_arg (dst, arg) |

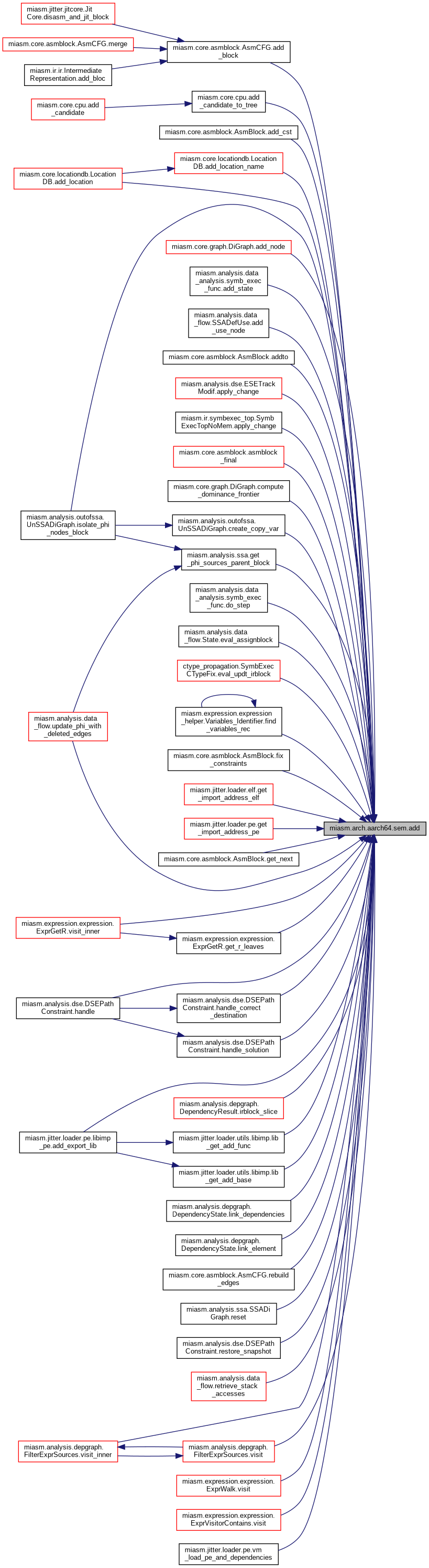

| def | add (arg1, arg2, arg3) |

| def | sub (arg1, arg2, arg3) |

| def | neg (arg1, arg2) |

| def | and_l (arg1, arg2, arg3) |

| def | eor (arg1, arg2, arg3) |

| def | eon (arg1, arg2, arg3) |

| def | orr (arg1, arg2, arg3) |

| def | orn (arg1, arg2, arg3) |

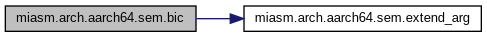

| def | bic (arg1, arg2, arg3) |

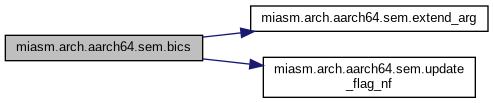

| def | bics (ir, instr, arg1, arg2, arg3) |

| def | mvn (arg1, arg2) |

| def | adds (ir, instr, arg1, arg2, arg3) |

| def | subs (ir, instr, arg1, arg2, arg3) |

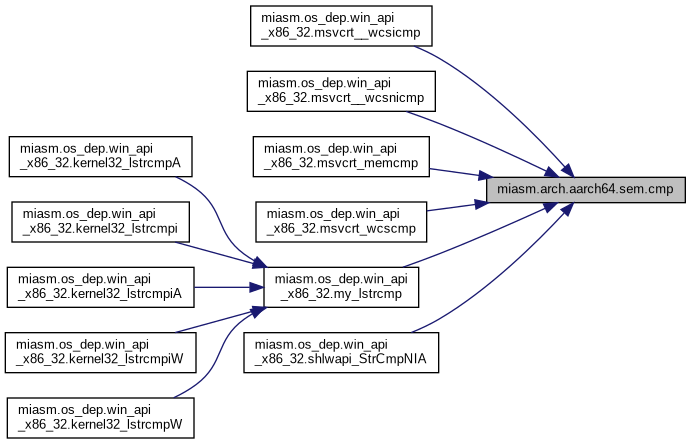

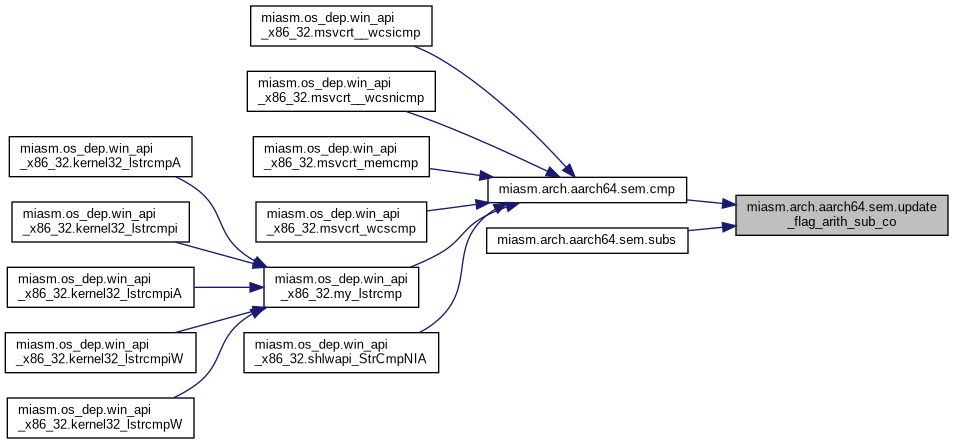

| def | cmp (ir, instr, arg1, arg2) |

| def | cmn (ir, instr, arg1, arg2) |

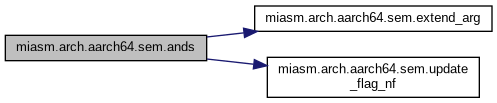

| def | ands (ir, instr, arg1, arg2, arg3) |

| def | tst (ir, instr, arg1, arg2) |

| def | lsl (arg1, arg2, arg3) |

| def | lsr (arg1, arg2, arg3) |

| def | asr (arg1, arg2, arg3) |

| def | mov (arg1, arg2) |

| def | movk (ir, instr, arg1, arg2) |

| def | movz (arg1, arg2) |

| def | movn (arg1, arg2) |

| def | bl (arg1) |

| def | csel (arg1, arg2, arg3, arg4) |

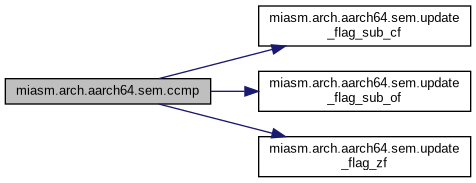

| def | ccmp (ir, instr, arg1, arg2, arg3, arg4) |

| def | csinc (ir, instr, arg1, arg2, arg3, arg4) |

| def | csinv (ir, instr, arg1, arg2, arg3, arg4) |

| def | csneg (ir, instr, arg1, arg2, arg3, arg4) |

| def | cset (ir, instr, arg1, arg2) |

| def | csetm (ir, instr, arg1, arg2) |

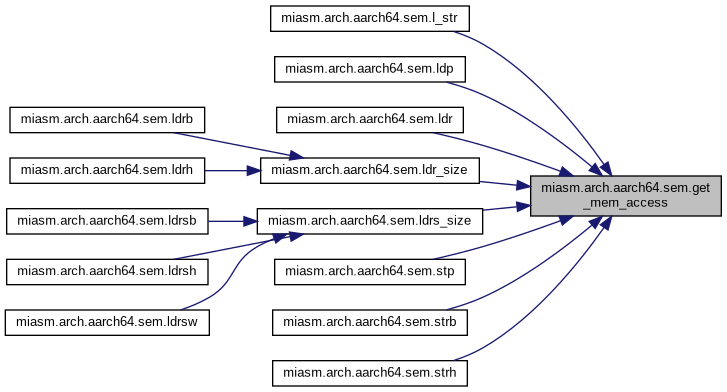

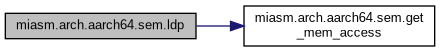

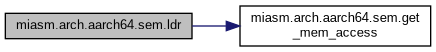

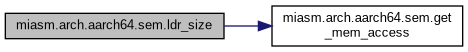

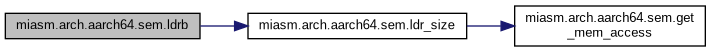

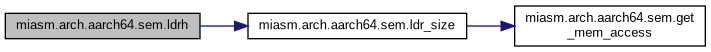

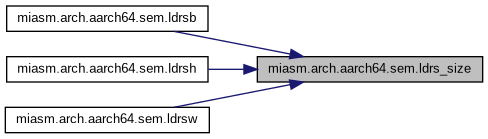

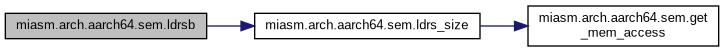

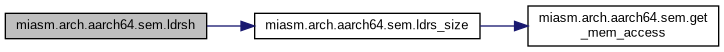

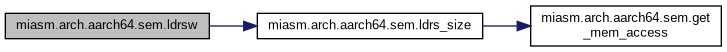

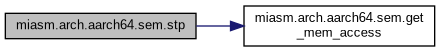

| def | get_mem_access (mem) |

| def | ldr (ir, instr, arg1, arg2) |

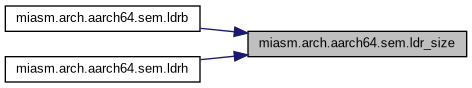

| def | ldr_size (ir, instr, arg1, arg2, size) |

| def | ldrb (ir, instr, arg1, arg2) |

| def | ldrh (ir, instr, arg1, arg2) |

| def | ldrs_size (ir, instr, arg1, arg2, size) |

| def | ldrsb (ir, instr, arg1, arg2) |

| def | ldrsh (ir, instr, arg1, arg2) |

| def | ldrsw (ir, instr, arg1, arg2) |

| def | ldaxrb (ir, instr, arg1, arg2) |

| def | stlxrb (ir, instr, arg1, arg2, arg3) |

| def | l_str (ir, instr, arg1, arg2) |

| def | strb (ir, instr, arg1, arg2) |

| def | strh (ir, instr, arg1, arg2) |

| def | stp (ir, instr, arg1, arg2, arg3) |

| def | ldp (ir, instr, arg1, arg2, arg3) |

| def | sbfm (ir, instr, arg1, arg2, arg3, arg4) |

| def | ubfm (ir, instr, arg1, arg2, arg3, arg4) |

| def | bfm (ir, instr, arg1, arg2, arg3, arg4) |

| def | mrs (ir, insr, arg1, arg2, arg3, arg4, arg5, arg6) |

| def | msr (ir, instr, arg1, arg2, arg3, arg4, arg5, arg6) |

| def | adc (ir, instr, arg1, arg2, arg3) |

| def | adcs (ir, instr, arg1, arg2, arg3) |

| def | sbc (ir, instr, arg1, arg2, arg3) |

| def | sbcs (ir, instr, arg1, arg2, arg3) |

| def | madd (arg1, arg2, arg3, arg4) |

| def | msub (arg1, arg2, arg3, arg4) |

| def | udiv (arg1, arg2, arg3) |

| def | sdiv (arg1, arg2, arg3) |

| def | smaddl (arg1, arg2, arg3, arg4) |

| def | cbz (arg1, arg2) |

| def | cbnz (arg1, arg2) |

| def | tbz (arg1, arg2, arg3) |

| def | tbnz (arg1, arg2, arg3) |

| def | b_ne (arg1) |

| def | b_eq (arg1) |

| def | b_ge (arg1) |

| def | b_mi (arg1) |

| def | b_pl (arg1) |

| def | b_gt (arg1) |

| def | b_cc (arg1) |

| def | b_cs (arg1) |

| def | b_hi (arg1) |

| def | b_le (arg1) |

| def | b_ls (arg1) |

| def | b_lt (arg1) |

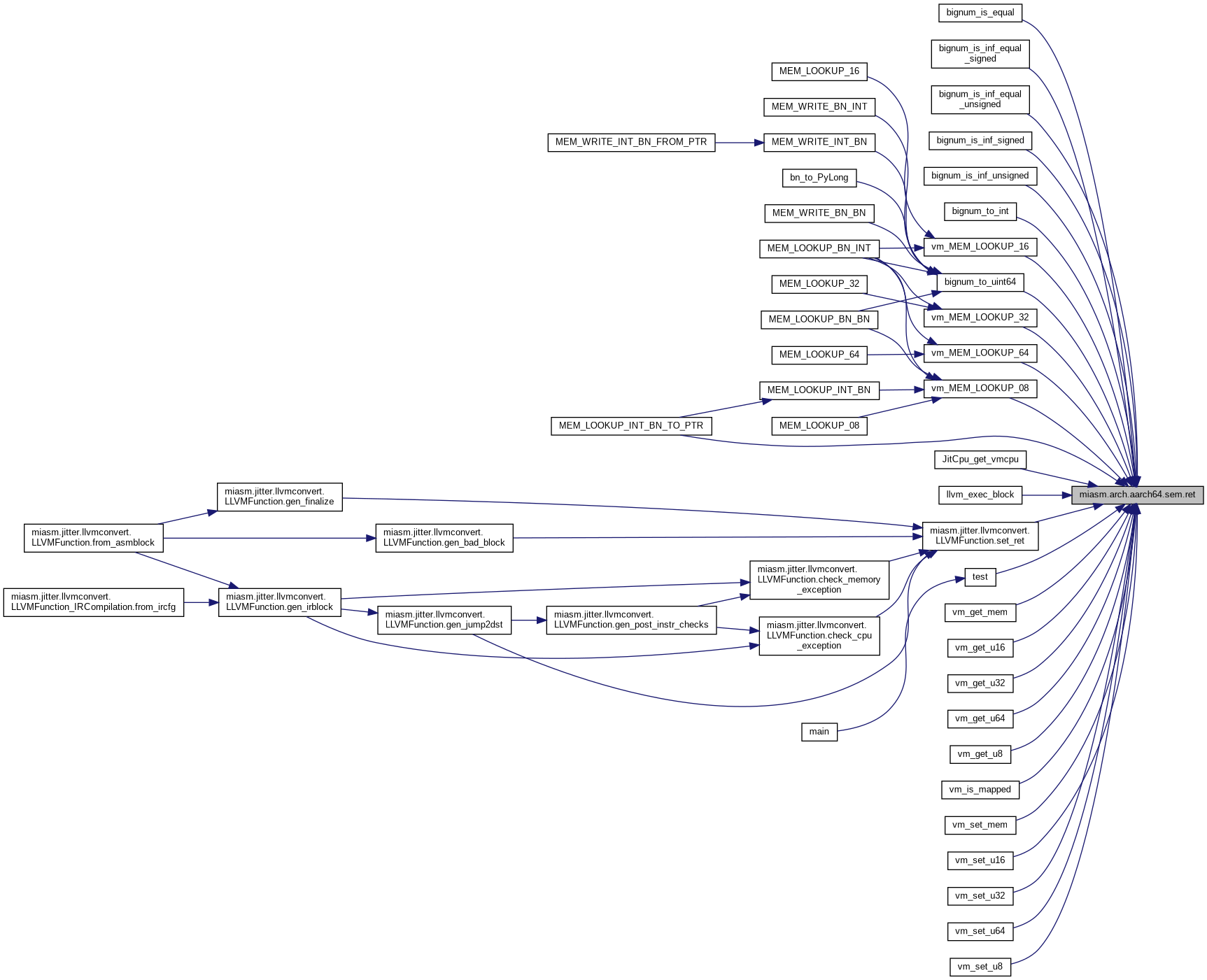

| def | ret (arg1) |

| def | adrp (arg1, arg2) |

| def | adr (arg1, arg2) |

| def | b (arg1) |

| def | br (arg1) |

| def | blr (arg1) |

| def | nop () |

| def | rev (ir, instr, arg1, arg2) |

| def | rev16 (ir, instr, arg1, arg2) |

| def | extr (arg1, arg2, arg3, arg4) |

| def | svc (arg1) |

| def | fmov (ir, instr, arg1, arg2) |

| def | fadd (ir, instr, arg1, arg2, arg3) |

| def | fsub (ir, instr, arg1, arg2, arg3) |

| def | fmul (ir, instr, arg1, arg2, arg3) |

| def | fdiv (ir, instr, arg1, arg2, arg3) |

| def | fabs (ir, instr, arg1, arg2) |

| def | fmadd (ir, instr, arg1, arg2, arg3, arg4) |

| def | fmsub (ir, instr, arg1, arg2, arg3, arg4) |

| def | fcvt (ir, instr, arg1, arg2) |

| def | scvtf (ir, instr, arg1, arg2) |

| def | ucvtf (ir, instr, arg1, arg2) |

| def | fcvtzs (ir, instr, arg1, arg2) |

| def | fcvtzu (ir, instr, arg1, arg2) |

| def | fcmpe (ir, instr, arg1, arg2) |

| def | clz (ir, instr, arg1, arg2) |

| def | casp (ir, instr, arg1, arg2, arg3) |

| def | umaddl (arg1, arg2, arg3, arg4) |

| def | umsubbl (arg1, arg2, arg3, arg4) |

| def | umull (arg1, arg2, arg3) |

| def | umulh (arg1, arg2, arg3) |

| def | smulh (arg1, arg2, arg3) |

| def | smull (arg1, arg2, arg3) |

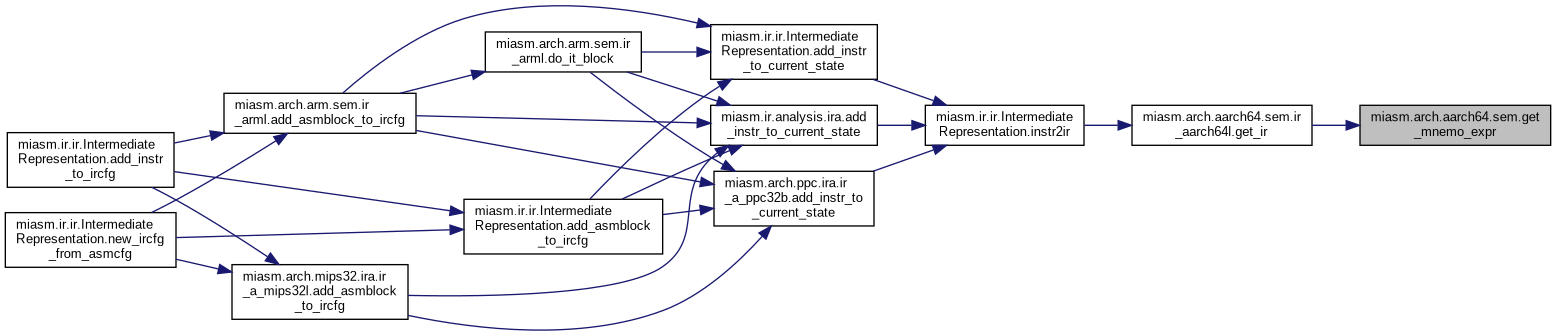

| def | get_mnemo_expr (ir, instr, *args) |

Variables | |

| dictionary | system_regs |

| dictionary | cond2expr |

| dictionary | ctx |

| sbuild = SemBuilder(ctx) | |

| mnemo_func = sbuild.functions | |

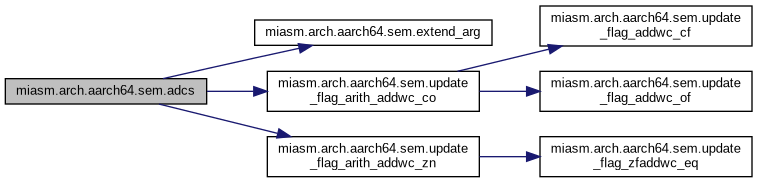

| def miasm.arch.aarch64.sem.adc | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.adcs | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

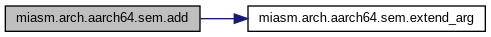

| def miasm.arch.aarch64.sem.add | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

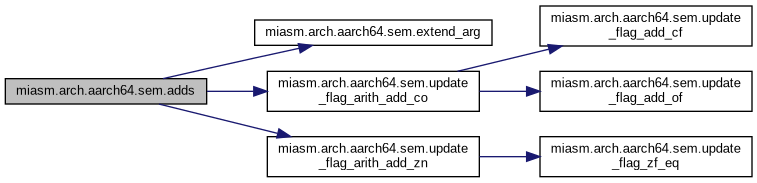

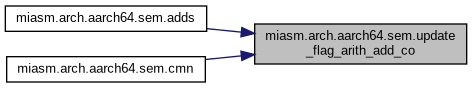

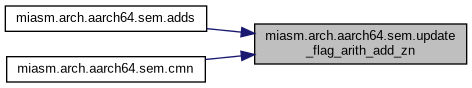

| def miasm.arch.aarch64.sem.adds | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.adr | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.adrp | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.and_l | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.ands | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.asr | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.b | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_cc | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_cs | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_eq | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_ge | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_gt | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_hi | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_le | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_ls | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_lt | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_mi | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_ne | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.b_pl | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.bfm | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.bic | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.bics | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.bl | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.blr | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.br | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.casp | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.cbnz | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.cbz | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ccmp | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.check_ops_msb | ( | a, | |

| b, | |||

| c | |||

| ) |

| def miasm.arch.aarch64.sem.clz | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.cmn | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.cmp | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.csel | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.cset | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.csetm | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.csinc | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.csinv | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.csneg | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.eon | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.eor | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.extend_arg | ( | dst, | |

| arg | |||

| ) |

| def miasm.arch.aarch64.sem.extr | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

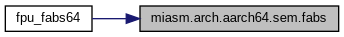

| def miasm.arch.aarch64.sem.fabs | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.fadd | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.fcmpe | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.fcvt | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.fcvtzs | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.fcvtzu | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.fdiv | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.fmadd | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.fmov | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.fmsub | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.fmul | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.fsub | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

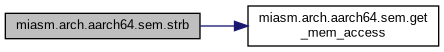

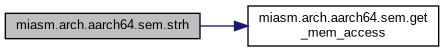

| def miasm.arch.aarch64.sem.get_mem_access | ( | mem | ) |

| def miasm.arch.aarch64.sem.get_mnemo_expr | ( | ir, | |

| instr, | |||

| * | args | ||

| ) |

| def miasm.arch.aarch64.sem.l_str | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ldaxrb | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ldp | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.ldr | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ldr_size | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| size | |||

| ) |

| def miasm.arch.aarch64.sem.ldrb | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ldrh | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ldrs_size | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| size | |||

| ) |

| def miasm.arch.aarch64.sem.ldrsb | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ldrsh | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ldrsw | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.lsl | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.lsr | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.madd | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.mov | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.movk | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.movn | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.movz | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.mrs | ( | ir, | |

| insr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4, | |||

| arg5, | |||

| arg6 | |||

| ) |

| def miasm.arch.aarch64.sem.msr | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4, | |||

| arg5, | |||

| arg6 | |||

| ) |

| def miasm.arch.aarch64.sem.msub | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.mvn | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.neg | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.nop | ( | ) |

Do nothing

| def miasm.arch.aarch64.sem.orn | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.orr | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.ret | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.rev | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.rev16 | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.sbc | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.sbcs | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.sbfm | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.scvtf | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.sdiv | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.smaddl | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.smulh | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.smull | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.stlxrb | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.stp | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.strb | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.strh | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.sub | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.subs | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.svc | ( | arg1 | ) |

| def miasm.arch.aarch64.sem.tbnz | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.tbz | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.tst | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.ubfm | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.ucvtf | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.aarch64.sem.udiv | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.umaddl | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.umsubbl | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.aarch64.sem.umulh | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.umull | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

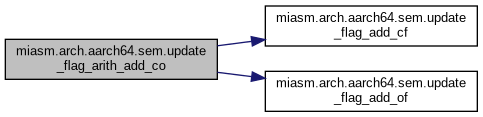

| def miasm.arch.aarch64.sem.update_flag_add_cf | ( | op1, | |

| op2 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_add_of | ( | op1, | |

| op2 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_addwc_cf | ( | op1, | |

| op2, | |||

| op3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_addwc_of | ( | op1, | |

| op2, | |||

| op3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_arith_add_co | ( | arg1, | |

| arg2 | |||

| ) |

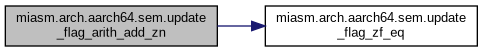

| def miasm.arch.aarch64.sem.update_flag_arith_add_zn | ( | arg1, | |

| arg2 | |||

| ) |

Compute zf and nf flags for (arg1 + arg2)

| def miasm.arch.aarch64.sem.update_flag_arith_addwc_co | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_arith_addwc_zn | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Compute znp flags for (arg1 + arg2 + cf)

| def miasm.arch.aarch64.sem.update_flag_arith_sub_co | ( | arg1, | |

| arg2 | |||

| ) |

Compute cf and of flags for (arg1 - arg2)

| def miasm.arch.aarch64.sem.update_flag_arith_sub_zn | ( | arg1, | |

| arg2 | |||

| ) |

Compute zf and nf flags for (arg1 - arg2)

| def miasm.arch.aarch64.sem.update_flag_arith_subwc_co | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_arith_subwc_zn | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Compute znp flags for (arg1 - (arg2 + cf))

| def miasm.arch.aarch64.sem.update_flag_nf | ( | arg | ) |

| def miasm.arch.aarch64.sem.update_flag_sub_cf | ( | op1, | |

| op2 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_sub_of | ( | op1, | |

| op2 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_subwc_cf | ( | op1, | |

| op2, | |||

| op3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_subwc_of | ( | op1, | |

| op2, | |||

| op3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_zf | ( | a | ) |

| def miasm.arch.aarch64.sem.update_flag_zf_eq | ( | a, | |

| b | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_zfaddwc_eq | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_zfsubwc_eq | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.aarch64.sem.update_flag_zn | ( | a | ) |

| dictionary miasm.arch.aarch64.sem.cond2expr |

| dictionary miasm.arch.aarch64.sem.ctx |

| miasm.arch.aarch64.sem.mnemo_func = sbuild.functions |

| miasm.arch.aarch64.sem.sbuild = SemBuilder(ctx) |

| dictionary miasm.arch.aarch64.sem.system_regs |