|

miasm

Reverse engineering framework

|

|

miasm

Reverse engineering framework

|

Classes | |

| class | ir_mips32b |

| class | ir_mips32l |

Functions | |

| def | addiu (arg1, arg2, arg3) |

| def | lw (arg1, arg2) |

| def | sw (arg1, arg2) |

| def | jal (arg1) |

| def | jalr (arg1, arg2) |

| def | bal (arg1) |

| def | l_b (arg1) |

| def | lbu (arg1, arg2) |

| def | lh (arg1, arg2) |

| def | lhu (arg1, arg2) |

| def | lb (arg1, arg2) |

| def | ll (arg1, arg2) |

| def | beq (arg1, arg2, arg3) |

| def | beql (arg1, arg2, arg3) |

| def | bgez (arg1, arg2) |

| def | bgezl (arg1, arg2) |

| def | bne (arg1, arg2, arg3) |

| def | bnel (arg1, arg2, arg3) |

| def | lui (arg1, arg2) |

| def | nop () |

| def | sync (arg1) |

| def | pref (arg1, arg2) |

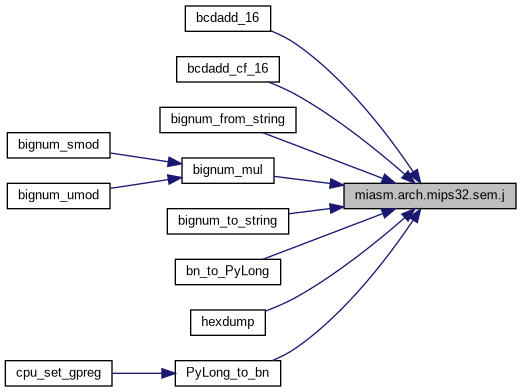

| def | j (arg1) |

| def | l_or (arg1, arg2, arg3) |

| def | nor (arg1, arg2, arg3) |

| def | l_and (arg1, arg2, arg3) |

| def | ext (arg1, arg2, arg3, arg4) |

| def | mul (arg1, arg2, arg3) |

| def | sltu (arg1, arg2, arg3) |

| def | slt (arg1, arg2, arg3) |

| def | l_sub (arg1, arg2, arg3) |

| def | sb (arg1, arg2) |

| def | sh (arg1, arg2) |

| def | movn (arg1, arg2, arg3) |

| def | movz (arg1, arg2, arg3) |

| def | srl (arg1, arg2, arg3) |

| def | sra (arg1, arg2, arg3) |

| def | srav (arg1, arg2, arg3) |

| def | sll (arg1, arg2, arg3) |

| def | srlv (arg1, arg2, arg3) |

| def | sllv (arg1, arg2, arg3) |

| def | l_xor (arg1, arg2, arg3) |

| def | seb (arg1, arg2) |

| def | seh (arg1, arg2) |

| def | bltz (arg1, arg2) |

| def | bltzl (arg1, arg2) |

| def | blez (arg1, arg2) |

| def | blezl (arg1, arg2) |

| def | bgtz (arg1, arg2) |

| def | bgtzl (arg1, arg2) |

| def | wsbh (arg1, arg2) |

| def | rotr (arg1, arg2, arg3) |

| def | add_d (arg1, arg2, arg3) |

| def | sub_d (arg1, arg2, arg3) |

| def | div_d (arg1, arg2, arg3) |

| def | mul_d (arg1, arg2, arg3) |

| def | mov_d (arg1, arg2) |

| def | mfc0 (arg1, arg2) |

| def | mfc1 (arg1, arg2) |

| def | mtc0 (arg1, arg2) |

| def | mtc1 (arg1, arg2) |

| def | tlbwi () |

| def | tlbp () |

| def | tlbwr () |

| def | tlbr () |

| def | ins (ir, instr, a, b, c, d) |

| def | lwc1 (arg1, arg2) |

| def | swc1 (arg1, arg2) |

| def | c_lt_d (arg1, arg2, arg3) |

| def | c_eq_d (arg1, arg2, arg3) |

| def | c_le_d (arg1, arg2, arg3) |

| def | bc1t (arg1, arg2) |

| def | bc1tl (arg1, arg2) |

| def | bc1f (arg1, arg2) |

| def | bc1fl (arg1, arg2) |

| def | cvt_d_w (arg1, arg2) |

| def | mult (arg1, arg2) |

| def | multu (arg1, arg2) |

| def | div (arg1, arg2) |

| def | divu (arg1, arg2) |

| def | mfhi (arg1) |

| def | mflo (arg1) |

| def | di (arg1) |

| def | ei (arg1) |

| def | ehb (arg1) |

| def | sc (arg1, arg2) |

| def | mthi (arg1) |

| def | mtlo (arg1) |

| def | clz (ir, instr, rs, rd) |

| def | teq (ir, instr, arg1, arg2) |

| def | tne (ir, instr, arg1, arg2) |

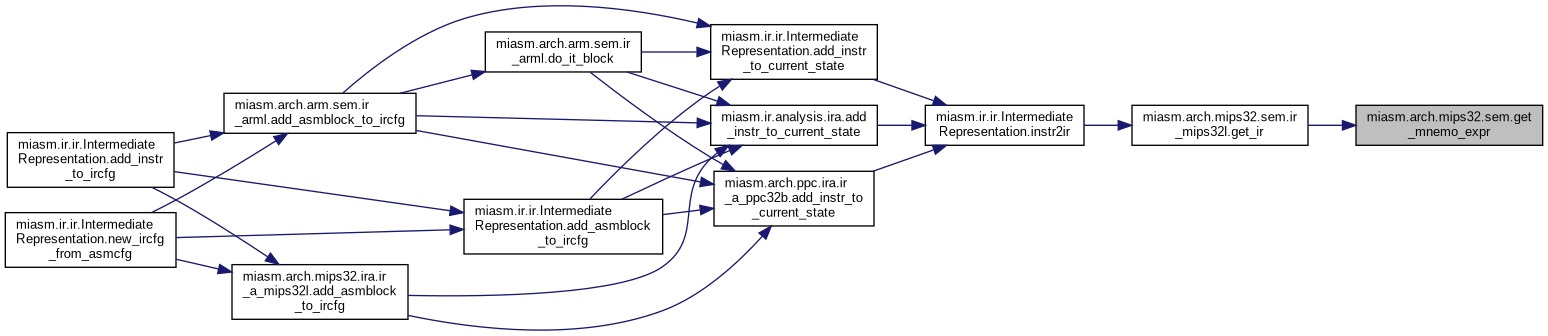

| def | get_mnemo_expr (ir, instr, *args) |

Variables | |

| dictionary | ctx |

| sbuild = SemBuilder(ctx) | |

| mnemo_func = sbuild.functions | |

| def miasm.arch.mips32.sem.add_d | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.addiu | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Adds a register @arg3 and a sign-extended immediate value @arg2 and stores the result in a register @arg1

| def miasm.arch.mips32.sem.bal | ( | arg1 | ) |

| def miasm.arch.mips32.sem.bc1f | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.bc1fl | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.bc1t | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.bc1tl | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.beq | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.beql | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.bgez | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the quantities of register @arg1 is greater than or equal to zero

| def miasm.arch.mips32.sem.bgezl | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the quantities of register @arg1 is greater than or equal to zero

| def miasm.arch.mips32.sem.bgtz | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the register @arg1 is greater than zero

| def miasm.arch.mips32.sem.bgtzl | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the register @arg1 is greater than zero

| def miasm.arch.mips32.sem.blez | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the register @arg1 is less than or equal to zero

| def miasm.arch.mips32.sem.blezl | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the register @arg1 is less than or equal to zero

| def miasm.arch.mips32.sem.bltz | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the register @arg1 is less than zero

| def miasm.arch.mips32.sem.bltzl | ( | arg1, | |

| arg2 | |||

| ) |

Branches on @arg2 if the register @arg1 is less than zero

| def miasm.arch.mips32.sem.bne | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Branches on @arg3 if the quantities of two registers @arg1, @arg2 are NOT equal

| def miasm.arch.mips32.sem.bnel | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Branches on @arg3 if the quantities of two registers @arg1, @arg2 are NOT equal

| def miasm.arch.mips32.sem.c_eq_d | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.c_le_d | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.c_lt_d | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.clz | ( | ir, | |

| instr, | |||

| rs, | |||

| rd | |||

| ) |

| def miasm.arch.mips32.sem.cvt_d_w | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.di | ( | arg1 | ) |

| def miasm.arch.mips32.sem.div | ( | arg1, | |

| arg2 | |||

| ) |

Divide (signed) @arg1 by @arg2 and stores the remaining/result in $R_HI/$R_LO

| def miasm.arch.mips32.sem.div_d | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.divu | ( | arg1, | |

| arg2 | |||

| ) |

Divide (unsigned) @arg1 by @arg2 and stores the remaining/result in $R_HI/$R_LO

| def miasm.arch.mips32.sem.ehb | ( | arg1 | ) |

| def miasm.arch.mips32.sem.ei | ( | arg1 | ) |

| def miasm.arch.mips32.sem.ext | ( | arg1, | |

| arg2, | |||

| arg3, | |||

| arg4 | |||

| ) |

| def miasm.arch.mips32.sem.get_mnemo_expr | ( | ir, | |

| instr, | |||

| * | args | ||

| ) |

| def miasm.arch.mips32.sem.ins | ( | ir, | |

| instr, | |||

| a, | |||

| b, | |||

| c, | |||

| d | |||

| ) |

| def miasm.arch.mips32.sem.j | ( | arg1 | ) |

Jump to an address @arg1

| def miasm.arch.mips32.sem.jal | ( | arg1 | ) |

| def miasm.arch.mips32.sem.jalr | ( | arg1, | |

| arg2 | |||

| ) |

Jump to an address stored in a register @arg1, and store the return address in another register @arg2

| def miasm.arch.mips32.sem.l_and | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Bitwise logical ands two registers @arg2, @arg3 and stores the result in a register @arg1

| def miasm.arch.mips32.sem.l_b | ( | arg1 | ) |

| def miasm.arch.mips32.sem.l_or | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Bitwise logical ors two registers @arg2, @arg3 and stores the result in a register @arg1

| def miasm.arch.mips32.sem.l_sub | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.l_xor | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Exclusive ors two registers @arg2, @arg3 and stores the result in a register @arg3

| def miasm.arch.mips32.sem.lb | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.lbu | ( | arg1, | |

| arg2 | |||

| ) |

A byte is loaded (unsigned extended) into a register @arg1 from the specified address @arg2.

| def miasm.arch.mips32.sem.lh | ( | arg1, | |

| arg2 | |||

| ) |

A word is loaded into a register @arg1 from the specified address @arg2.

| def miasm.arch.mips32.sem.lhu | ( | arg1, | |

| arg2 | |||

| ) |

A word is loaded (unsigned extended) into a register @arg1 from the specified address @arg2.

| def miasm.arch.mips32.sem.ll | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.lui | ( | arg1, | |

| arg2 | |||

| ) |

The immediate value @arg2 is shifted left 16 bits and stored in the register @arg1. The lower 16 bits are zeroes.

| def miasm.arch.mips32.sem.lw | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.lwc1 | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.mfc0 | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.mfc1 | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.mfhi | ( | arg1 | ) |

| def miasm.arch.mips32.sem.mflo | ( | arg1 | ) |

| def miasm.arch.mips32.sem.mov_d | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.movn | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.movz | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.mtc0 | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.mtc1 | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.mthi | ( | arg1 | ) |

| def miasm.arch.mips32.sem.mtlo | ( | arg1 | ) |

| def miasm.arch.mips32.sem.mul | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Multiplies @arg2 by $arg3 and stores the result in @arg1.

| def miasm.arch.mips32.sem.mul_d | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.mult | ( | arg1, | |

| arg2 | |||

| ) |

Multiplies (signed) @arg1 by @arg2 and stores the result in $R_HI:$R_LO

| def miasm.arch.mips32.sem.multu | ( | arg1, | |

| arg2 | |||

| ) |

Multiplies (unsigned) @arg1 by @arg2 and stores the result in $R_HI:$R_LO

| def miasm.arch.mips32.sem.nop | ( | ) |

Do nothing

| def miasm.arch.mips32.sem.nor | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Bitwise logical Nors two registers @arg2, @arg3 and stores the result in a register @arg1

| def miasm.arch.mips32.sem.pref | ( | arg1, | |

| arg2 | |||

| ) |

To move data between memory and cache

| def miasm.arch.mips32.sem.rotr | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.sb | ( | arg1, | |

| arg2 | |||

| ) |

The least significant byte of @arg1 is stored at the specified address @arg2.

| def miasm.arch.mips32.sem.sc | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.seb | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.seh | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.sh | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.sll | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.sllv | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Shifts a register value @arg2 left by the amount specified in @arg3 and places the value in the destination register @arg1. Zeroes are shifted in.

| def miasm.arch.mips32.sem.slt | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

If @arg2 is less than @arg3 (signed), @arg1 is set to one. It gets zero otherwise.

| def miasm.arch.mips32.sem.sltu | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

If @arg2 is less than @arg3 (unsigned), @arg1 is set to one. It gets zero otherwise.

| def miasm.arch.mips32.sem.sra | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Shifts arg1 register value @arg2 right by the shift amount @arg3 and places the value in the destination register @arg1. The sign bit is shifted in.

| def miasm.arch.mips32.sem.srav | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.srl | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Shifts arg1 register value @arg2 right by the shift amount @arg3 and places the value in the destination register @arg1. Zeroes are shifted in.

| def miasm.arch.mips32.sem.srlv | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

Shifts a register value @arg2 right by the amount specified in @arg3 and places the value in the destination register @arg1. Zeroes are shifted in.

| def miasm.arch.mips32.sem.sub_d | ( | arg1, | |

| arg2, | |||

| arg3 | |||

| ) |

| def miasm.arch.mips32.sem.sw | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.swc1 | ( | arg1, | |

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.sync | ( | arg1 | ) |

Synchronize Shared Memory

| def miasm.arch.mips32.sem.teq | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.tlbp | ( | ) |

| def miasm.arch.mips32.sem.tlbr | ( | ) |

| def miasm.arch.mips32.sem.tlbwi | ( | ) |

| def miasm.arch.mips32.sem.tlbwr | ( | ) |

| def miasm.arch.mips32.sem.tne | ( | ir, | |

| instr, | |||

| arg1, | |||

| arg2 | |||

| ) |

| def miasm.arch.mips32.sem.wsbh | ( | arg1, | |

| arg2 | |||

| ) |

| dictionary miasm.arch.mips32.sem.ctx |

| miasm.arch.mips32.sem.mnemo_func = sbuild.functions |

| miasm.arch.mips32.sem.sbuild = SemBuilder(ctx) |