|

miasm

Reverse engineering framework

|

|

miasm

Reverse engineering framework

|

Functions | |

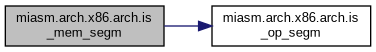

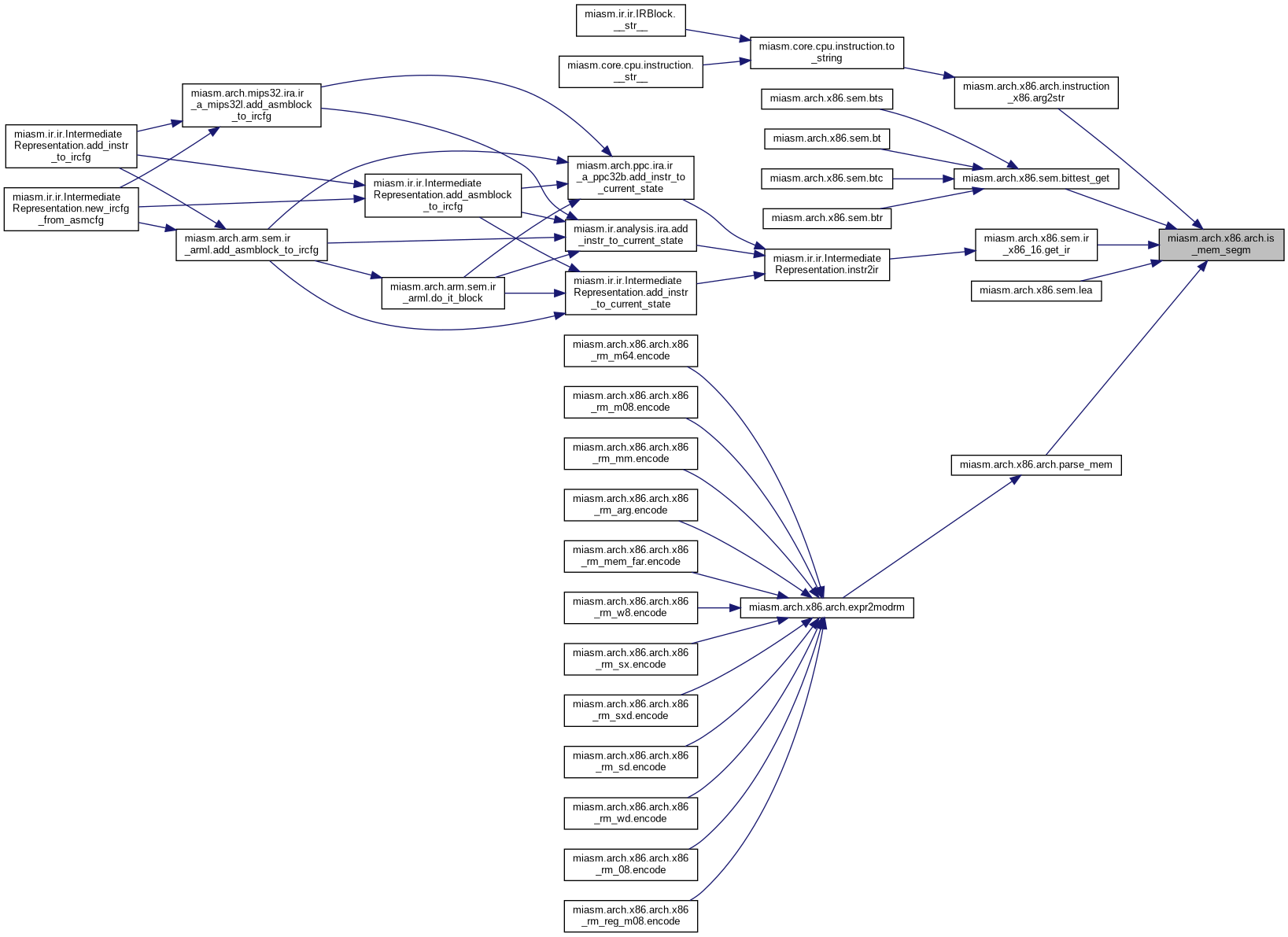

| def | is_op_segm (expr) |

| def | is_mem_segm (expr) |

| def | cb_deref_segmoff (tokens) |

| def | cb_deref_base_expr (tokens) |

| def | cb_deref_mem (tokens) |

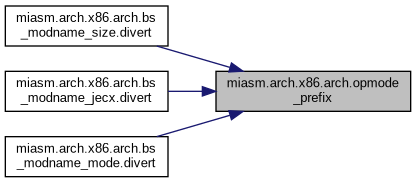

| def | opmode_prefix (mode) |

| def | admode_prefix (mode) |

| def | v_opmode_info (size, opmode, rex_w, stk) |

| def | v_opmode (p) |

| def | v_admode_info (size, admode) |

| def | v_admode (p) |

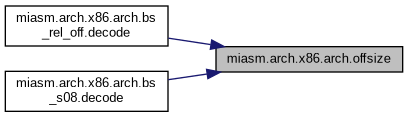

| def | offsize (p) |

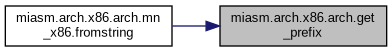

| def | get_prefix (s) |

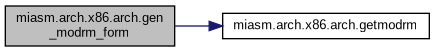

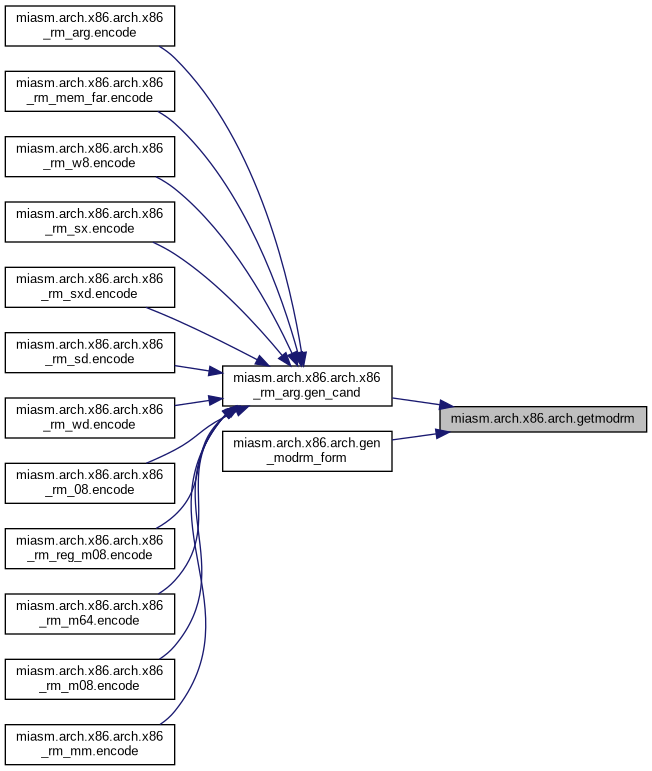

| def | getmodrm (c) |

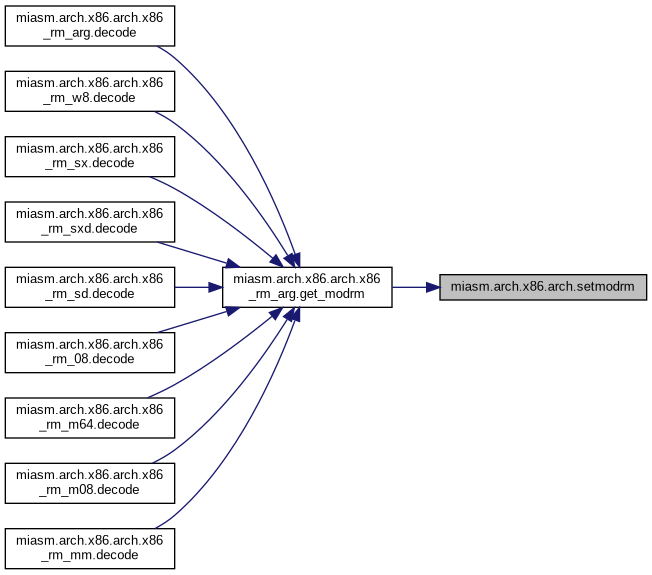

| def | setmodrm (mod, re, rm) |

| def | sib (c) |

| def | gen_modrm_form () |

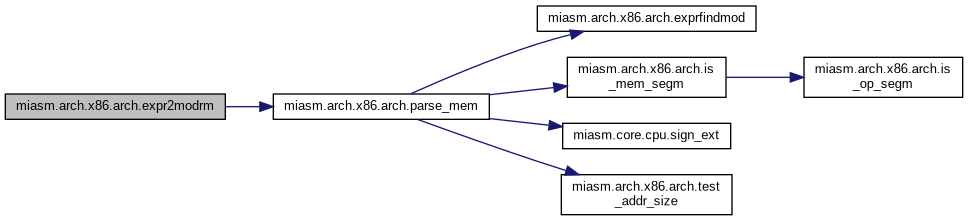

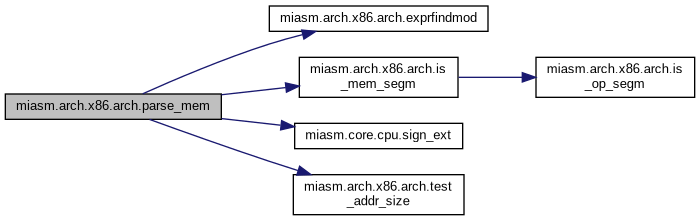

| def | exprfindmod (e, o=None) |

| def | test_addr_size (ptr, size) |

| def | parse_mem (expr, parent, w8, sx=0, xmm=0, mm=0, bnd=0) |

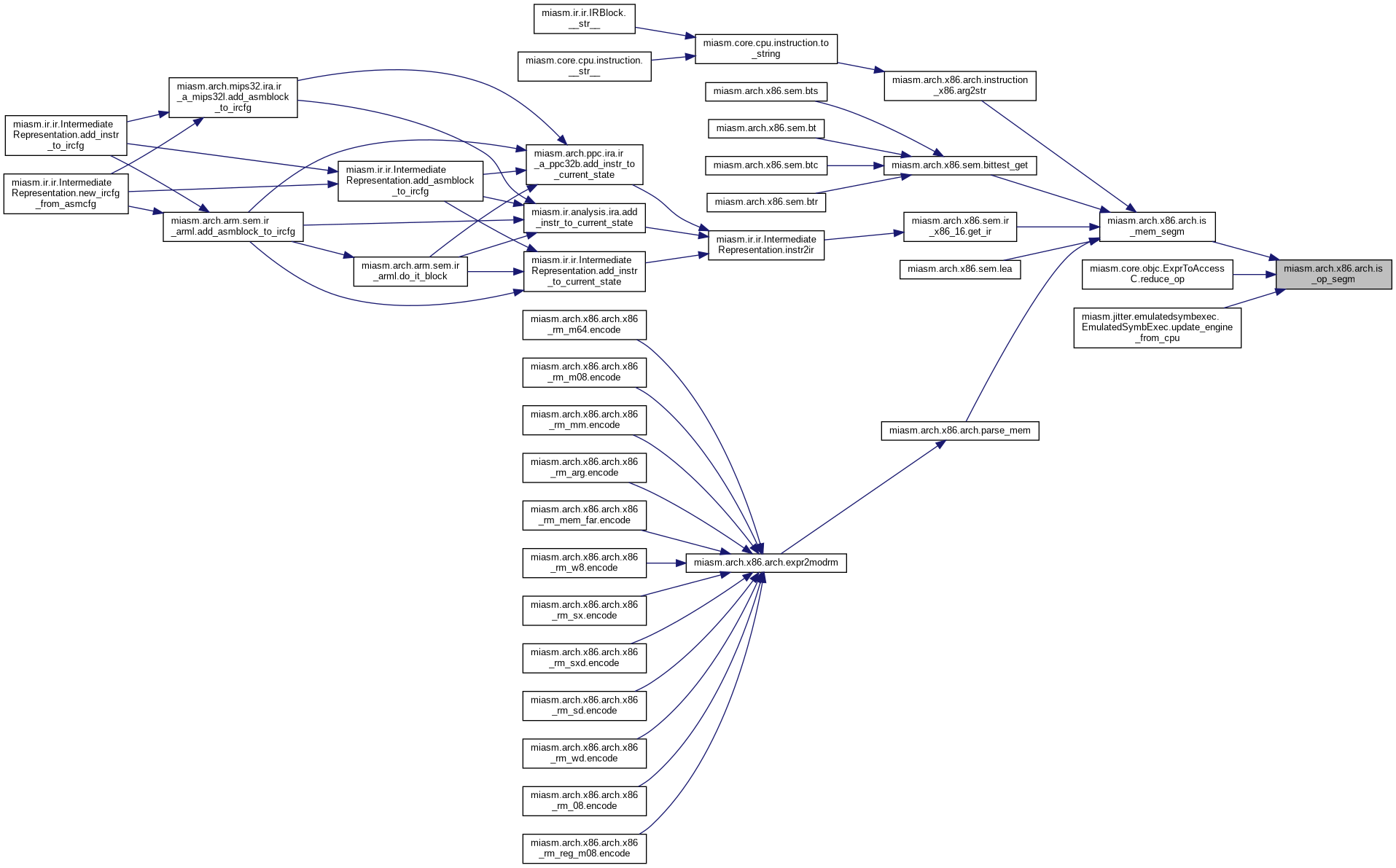

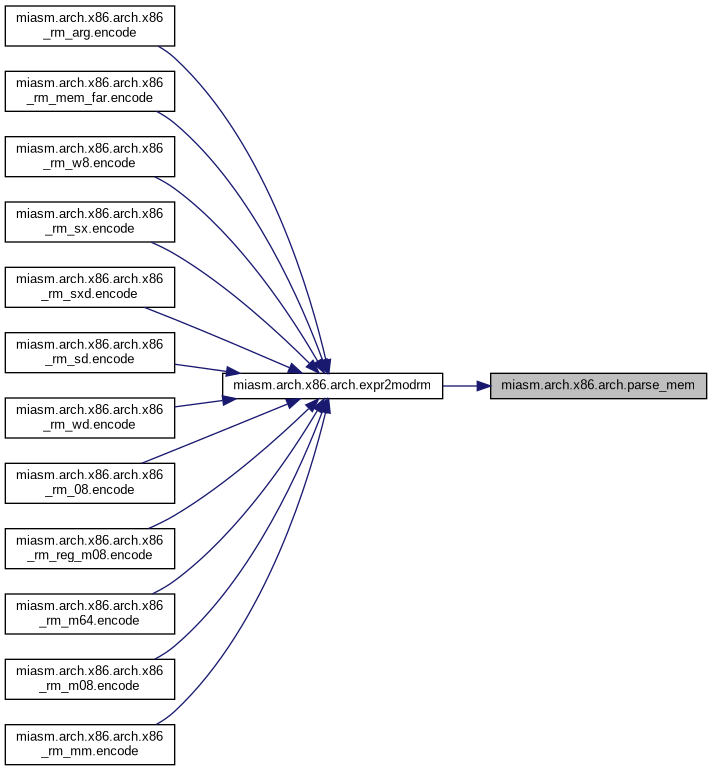

| def | expr2modrm (expr, parent, w8, sx=0, xmm=0, mm=0, bnd=0) |

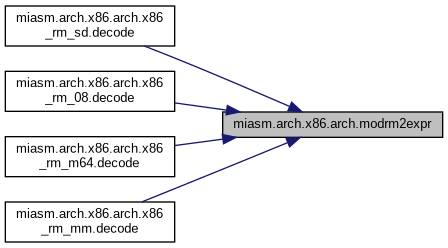

| def | modrm2expr (modrm, parent, w8, sx=0, xmm=0, mm=0, bnd=0) |

| def | sib_cond (cls, mode, v) |

| def | rmmod (r, rm_arg_x=rm_arg, modrm=mod) |

| def | addop (name, fields, args=None, alias=False) |

| def | print_size (e) |

Variables | |

| log = logging.getLogger("x86_arch") | |

| console_handler = logging.StreamHandler() | |

| list | conditional_branch |

| list | unconditional_branch = ['JMP', 'JMPF'] |

| string | f_isad = "AD" |

| string | f_s08 = "S08" |

| string | f_u08 = "U08" |

| string | f_s16 = "S16" |

| string | f_u16 = "U16" |

| string | f_s32 = "S32" |

| string | f_u32 = "U32" |

| string | f_s64 = "S64" |

| string | f_u64 = "U64" |

| string | f_imm = 'IMM' |

| dictionary | f_imm2size |

| dictionary | size2gpregs |

| dictionary | replace_regs64 |

| dictionary | replace_regs32 |

| dictionary | replace_regs16 |

| dictionary | replace_regs |

| dictionary | segm2enc = {CS: 1, SS: 2, DS: 3, ES: 4, FS: 5, GS: 6} |

| enc2segm = dict((value, key) for key, value in viewitems(segm2enc)) | |

| segm_info = reg_info_dct(enc2segm) | |

| dictionary | enc2crx |

| crx_info = reg_info_dct(enc2crx) | |

| dictionary | enc2drx |

| drx_info = reg_info_dct(enc2drx) | |

| PLUS = Suppress("+") | |

| MULT = Suppress("*") | |

| COLON = Suppress(":") | |

| LBRACK = Suppress("[") | |

| RBRACK = Suppress("]") | |

| tuple | gpreg |

| tuple | deref_mem_ad = (LBRACK + base_expr + RBRACK).setParseAction(cb_deref_base_expr) |

| tuple | deref_ptr = (base_expr + COLON + base_expr).setParseAction(cb_deref_segmoff) |

| PTR = Suppress('PTR') | |

| FAR = Suppress('FAR') | |

| BYTE = Literal('BYTE') | |

| WORD = Literal('WORD') | |

| DWORD = Literal('DWORD') | |

| QWORD = Literal('QWORD') | |

| TBYTE = Literal('TBYTE') | |

| XMMWORD = Literal('XMMWORD') | |

| dictionary | MEMPREFIX2SIZE |

| SIZE2MEMPREFIX = dict((value, key) for key, value in viewitems(MEMPREFIX2SIZE)) | |

| tuple | mem_size = (BYTE | DWORD | QWORD | WORD | TBYTE | XMMWORD) |

| tuple | deref_mem = (mem_size + PTR + Optional((base_expr + COLON))+ deref_mem_ad).setParseAction(cb_deref_mem) |

| tuple | rmarg |

| tuple | mem_far = FAR + deref_mem |

| cl_or_imm = r08_ecx.parser | |

| dictionary | invmode = {16: 32, 32: 16} |

| list | repeat_mn |

| list | db_afs_64 = [] |

| list | sib_64_s08_ebp = [] |

| dictionary | SIZE2XMMREG |

| dictionary | SIZE2BNDREG |

| d_rex_p = bs(l=0, cls=(bs_fbit,), fname="rex_p") | |

| d_rex_w = bs(l=0, cls=(bs_fbit,), fname="rex_w") | |

| d_rex_r = bs(l=0, cls=(bs_fbit,), fname="rex_r") | |

| d_rex_x = bs(l=0, cls=(bs_fbit,), fname="rex_x") | |

| d_rex_b = bs(l=0, cls=(bs_fbit,), fname="rex_b") | |

| d_g1 = bs(l=0, cls=(bs_fbit,), fname="g1") | |

| d_g2 = bs(l=0, cls=(bs_fbit,), fname="g2") | |

| d_cl1 = bs(l=1, cls=(bs_cl1,), fname="cl1") | |

| w8 = bs(l=1, fname="w8") | |

| se = bs(l=1, fname="se") | |

| sx = bs(l=0, fname="sx") | |

| sxd = bs(l=0, fname="sx") | |

| xmmreg = bs(l=0, fname="xmmreg") | |

| mmreg = bs(l=0, fname="mmreg") | |

| pref_f2 = bs(l=0, fname="prefixed", default=b"\xf2") | |

| pref_f3 = bs(l=0, fname="prefixed", default=b"\xf3") | |

| pref_66 = bs(l=0, fname="prefixed", default=b"\x66") | |

| no_xmm_pref = bs(l=0, fname="no_xmm_pref") | |

| no_rex = bs(l=0, fname="no_rex") | |

| sib_scale = bs(l=2, cls=(bs_cond_scale,), fname = "sib_scale") | |

| sib_index = bs(l=3, cls=(bs_cond_index,), fname = "sib_index") | |

| sib_base = bs(l=3, cls=(bs_cond_index,), fname = "sib_base") | |

| disp = bs(l=0, cls=(bs_cond_disp,), fname = "disp") | |

| s08 = bs(l=8, cls=(bs_s08, )) | |

| u08 = bs(l=8, cls=(x86_08, x86_arg)) | |

| u07 = bs(l=7, cls=(x86_08, x86_arg)) | |

| u16 = bs(l=16, cls=(x86_16, x86_arg)) | |

| u32 = bs(l=32, cls=(x86_32, x86_arg)) | |

| s3264 = bs(l=32, cls=(x86_s32to64, x86_arg)) | |

| u08_3 = bs(l=0, cls=(x86_imm_fix_08, x86_arg), ival = 3) | |

| d0 = bs("000", fname='reg') | |

| d1 = bs("001", fname='reg') | |

| d2 = bs("010", fname='reg') | |

| d3 = bs("011", fname='reg') | |

| d4 = bs("100", fname='reg') | |

| d5 = bs("101", fname='reg') | |

| d6 = bs("110", fname='reg') | |

| d7 = bs("111", fname='reg') | |

| sd = bs(l=1, fname="sd") | |

| wd = bs(l=1, fname="wd") | |

| stk = bs(l=0, fname="stk") | |

| d_imm64 = bs(l=0, fname="imm64") | |

| d_eax = bs(l=0, cls=(bs_eax, ), fname='eax') | |

| d_edx = bs(l=0, cls=(bs_edx, ), fname='edx') | |

| d_st = bs(l=0, cls=(x86_reg_st, ), fname='st') | |

| d_imm = bs(l=0, cls=(bs_cond_imm,), fname="imm") | |

| d_ax = bs(l=0, cls=(r_ax, ), fname='ax') | |

| d_dx = bs(l=0, cls=(r_dx, ), fname='dx') | |

| d_cl = bs(l=0, cls=(r_cl, ), fname='cl') | |

| d_cs = bs(l=0, cls=(bs_cs, ), fname='cs') | |

| d_ds = bs(l=0, cls=(bs_ds, ), fname='ds') | |

| d_es = bs(l=0, cls=(bs_es, ), fname='es') | |

| d_ss = bs(l=0, cls=(bs_ss, ), fname='ss') | |

| d_fs = bs(l=0, cls=(bs_fs, ), fname='fs') | |

| d_gs = bs(l=0, cls=(bs_gs, ), fname='gs') | |

| rel_off = bs(l=0, cls=(bs_rel_off,), fname="off", order=-1) | |

| rel_off08 = bs(l=8, cls=(bs_rel_off08,), fname="off", order=-1) | |

| moff = bs(l=0, cls=(bs_moff,), fname="off") | |

| msegoff = bs(l=16, cls=(bs_msegoff,), fname="mseg") | |

| movoff = bs(l=0, cls=(bs_movoff,), fname="off") | |

| mod = bs(l=2, fname="mod") | |

| mod_mem = bs(l=2, cls=(bs_mem,), fname="mod") | |

| mod_reg = bs(l=2, cls=(bs_reg,), fname="mod") | |

| rmreg = bs(l=3, cls=(x86_rm_reg, ), order =1, fname = "reg") | |

| reg = bs(l=3, cls=(x86_reg, ), order =1, fname = "reg") | |

| reg_modrm = bs(l=3, cls=(x86_reg_modrm, ), order =1, fname = "reg") | |

| regnoarg = bs(l=3, default_val="000", order=1, fname="reg") | |

| segm = bs(l=3, cls=(x86_rm_segm, ), order =1, fname = "reg") | |

| crreg = bs(l=3, cls=(x86_rm_cr, ), order =1, fname = "reg") | |

| drreg = bs(l=3, cls=(x86_rm_dr, ), order =1, fname = "reg") | |

| mm_reg = bs(l=3, cls=(x86_rm_reg_mm, ), order =1, fname = "reg") | |

| xmm_reg = bs(l=3, cls=(x86_rm_reg_xmm, ), order =1, fname = "reg") | |

| bnd_reg = bs(l=3, cls=(x86_rm_reg_bnd, ), order =1, fname = "reg") | |

| fltreg = bs(l=3, cls=(x86_rm_flt, ), order =1, fname = "reg") | |

| rm = bs(l=3, fname="rm") | |

| rm_arg = bs(l=0, cls=(x86_rm_arg,), fname='rmarg') | |

| rm_arg_w8 = bs(l=0, cls=(x86_rm_w8,), fname='rmarg') | |

| rm_arg_sx = bs(l=0, cls=(x86_rm_sx,), fname='rmarg') | |

| rm_arg_sxd = bs(l=0, cls=(x86_rm_sxd,), fname='rmarg') | |

| rm_arg_sd = bs(l=0, cls=(x86_rm_sd,), fname='rmarg') | |

| rm_arg_wd = bs(l=0, cls=(x86_rm_wd,), fname='rmarg') | |

| rm_arg_08 = bs(l=0, cls=(x86_rm_08,), fname='rmarg') | |

| rm_arg_reg_m08 = bs(l=0, cls=(x86_rm_reg_m08,), fname='rmarg') | |

| rm_arg_reg_m16 = bs(l=0, cls=(x86_rm_reg_m16,), fname='rmarg') | |

| rm_arg_m08 = bs(l=0, cls=(x86_rm_m08,), fname='rmarg') | |

| rm_arg_m64 = bs(l=0, cls=(x86_rm_m64,), fname='rmarg') | |

| rm_arg_m80 = bs(l=0, cls=(x86_rm_m80,), fname='rmarg') | |

| rm_arg_m16 = bs(l=0, cls=(x86_rm_m16,), fname='rmarg') | |

| rm_mem = bs(l=0, cls=(x86_rm_mem,), fname='rmarg') | |

| rm_mem_far = bs(l=0, cls=(x86_rm_mem_far,), fname='rmarg') | |

| rm_arg_mm = bs(l=0, cls=(x86_rm_mm,), fname='rmarg') | |

| rm_arg_mm_m64 = bs(l=0, cls=(x86_rm_mm_m64,), fname='rmarg') | |

| rm_arg_mm_reg = bs(l=0, cls=(x86_rm_mm_reg,), fname='rmarg') | |

| rm_arg_xmm = bs(l=0, cls=(x86_rm_xmm,), fname='rmarg') | |

| rm_arg_xmm_m32 = bs(l=0, cls=(x86_rm_xmm_m32,), fname='rmarg') | |

| rm_arg_xmm_m64 = bs(l=0, cls=(x86_rm_xmm_m64,), fname='rmarg') | |

| rm_arg_xmm_m128 = bs(l=0, cls=(x86_rm_xmm_m128,), fname='rmarg') | |

| rm_arg_xmm_reg = bs(l=0, cls=(x86_rm_xmm_reg,), fname='rmarg') | |

| rm_arg_bnd = bs(l=0, cls=(x86_rm_bnd,), fname='rmarg') | |

| rm_arg_bnd_m64 = bs(l=0, cls=(x86_rm_bnd_m64,), fname='rmarg') | |

| rm_arg_bnd_m128 = bs(l=0, cls=(x86_rm_bnd_m128,), fname='rmarg') | |

| rm_arg_bnd_reg = bs(l=0, cls=(x86_rm_bnd_reg,), fname='rmarg') | |

| swapargs = bs_swapargs(l=1, fname="swap", mn_mod=list(range(1 << 1))) | |

| bs_opmode16 = bs(l=0, cls=(bs_op_mode,), mode = 16, fname="fopmode") | |

| bs_opmode32 = bs(l=0, cls=(bs_op_mode,), mode = 32, fname="fopmode") | |

| bs_opmode64 = bs(l=0, cls=(bs_op_mode,), mode = 64, fname="fopmode") | |

| bs_admode16 = bs(l=0, cls=(bs_ad_mode,), mode = 16, fname="fadmode") | |

| bs_admode32 = bs(l=0, cls=(bs_ad_mode,), mode = 32, fname="fadmode") | |

| bs_admode64 = bs(l=0, cls=(bs_ad_mode,), mode = 64, fname="fadmode") | |

| bs_opmode16_no64 = bs(l=0, cls=(bs_op_mode_no64,), mode = 16, fname="fopmode") | |

| bs_opmode32_no64 = bs(l=0, cls=(bs_op_mode_no64,), mode = 32, fname="fopmode") | |

| bs_mode64 = bs(l=0, cls=(bs_op_mode64,)) | |

| bs_modeno64 = bs(l=0, cls=(bs_op_modeno64,)) | |

| list | cond_list |

| cond = bs_mod_name(l=4, fname='cond', mn_mod=cond_list) | |

| bintree | |

| MMX/SSE/AVX operations Categories are the same than here: https://software.intel.com/sites/landingpage/IntrinsicsGuide/. More... | |

| def miasm.arch.x86.arch.addop | ( | name, | |

| fields, | |||

args = None, |

|||

alias = False |

|||

| ) |

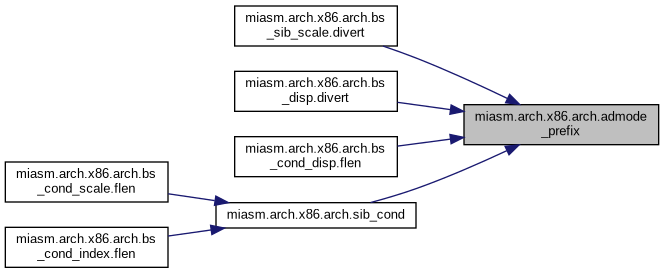

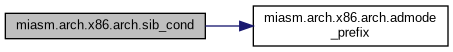

| def miasm.arch.x86.arch.admode_prefix | ( | mode | ) |

| def miasm.arch.x86.arch.cb_deref_base_expr | ( | tokens | ) |

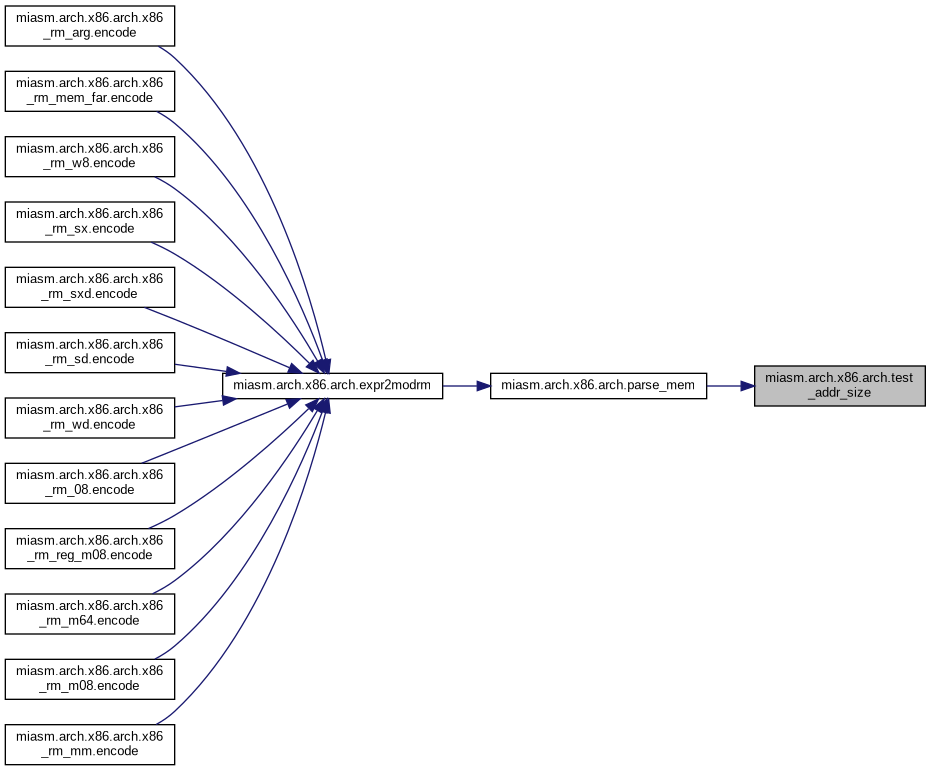

| def miasm.arch.x86.arch.cb_deref_mem | ( | tokens | ) |

| def miasm.arch.x86.arch.cb_deref_segmoff | ( | tokens | ) |

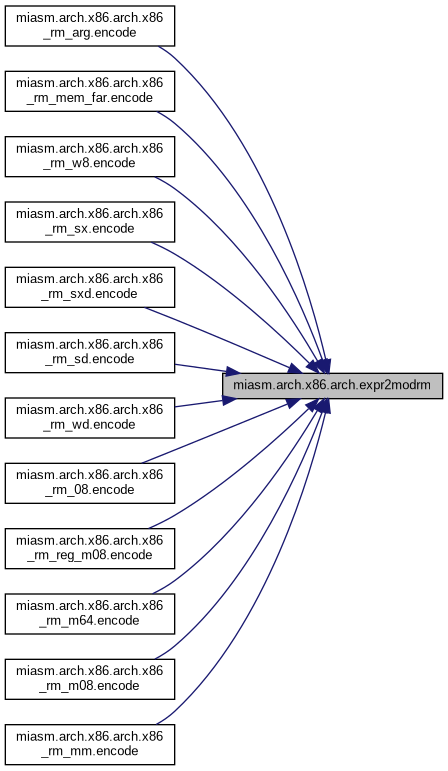

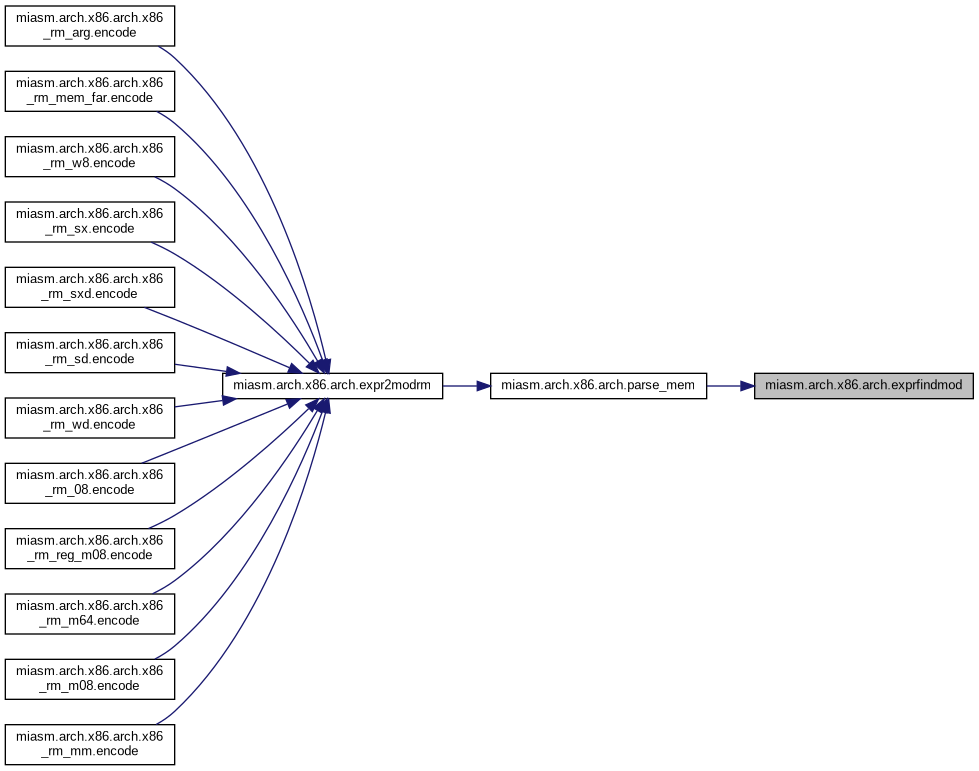

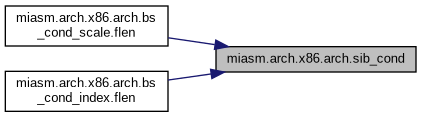

| def miasm.arch.x86.arch.expr2modrm | ( | expr, | |

| parent, | |||

| w8, | |||

sx = 0, |

|||

xmm = 0, |

|||

mm = 0, |

|||

bnd = 0 |

|||

| ) |

| def miasm.arch.x86.arch.exprfindmod | ( | e, | |

o = None |

|||

| ) |

| def miasm.arch.x86.arch.gen_modrm_form | ( | ) |

| def miasm.arch.x86.arch.get_prefix | ( | s | ) |

| def miasm.arch.x86.arch.getmodrm | ( | c | ) |

| def miasm.arch.x86.arch.is_mem_segm | ( | expr | ) |

Returns True if is ExprMem and ptr is_op_segm

| def miasm.arch.x86.arch.is_op_segm | ( | expr | ) |

Returns True if is ExprOp and op == 'segm'

| def miasm.arch.x86.arch.modrm2expr | ( | modrm, | |

| parent, | |||

| w8, | |||

sx = 0, |

|||

xmm = 0, |

|||

mm = 0, |

|||

bnd = 0 |

|||

| ) |

| def miasm.arch.x86.arch.offsize | ( | p | ) |

| def miasm.arch.x86.arch.opmode_prefix | ( | mode | ) |

| def miasm.arch.x86.arch.parse_mem | ( | expr, | |

| parent, | |||

| w8, | |||

sx = 0, |

|||

xmm = 0, |

|||

mm = 0, |

|||

bnd = 0 |

|||

| ) |

| def miasm.arch.x86.arch.print_size | ( | e | ) |

| def miasm.arch.x86.arch.setmodrm | ( | mod, | |

| re, | |||

| rm | |||

| ) |

| def miasm.arch.x86.arch.sib | ( | c | ) |

| def miasm.arch.x86.arch.sib_cond | ( | cls, | |

| mode, | |||

| v | |||

| ) |

| def miasm.arch.x86.arch.test_addr_size | ( | ptr, | |

| size | |||

| ) |

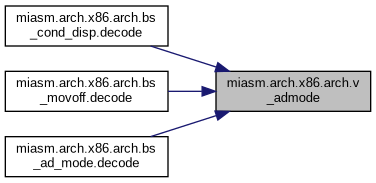

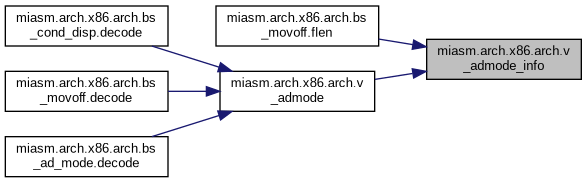

| def miasm.arch.x86.arch.v_admode | ( | p | ) |

| def miasm.arch.x86.arch.v_admode_info | ( | size, | |

| admode | |||

| ) |

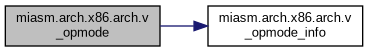

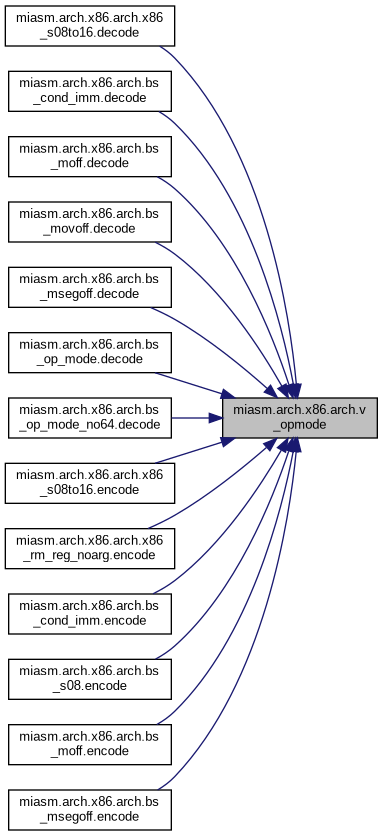

| def miasm.arch.x86.arch.v_opmode | ( | p | ) |

| def miasm.arch.x86.arch.v_opmode_info | ( | size, | |

| opmode, | |||

| rex_w, | |||

| stk | |||

| ) |

| miasm.arch.x86.arch.bintree |

MMX/SSE/AVX operations Categories are the same than here: https://software.intel.com/sites/landingpage/IntrinsicsGuide/.

Arithmetic (integers)

Move SSE

Additions SSE

Substractions SSE

Arithmetic (floating-point)

Additions SSE

Substractions SSE

Multiplications SSE

Divisions SSE

Logical (floating-point)

XOR

AND

OR

AND MMX

ANDN MMX

OR MMX

XOR MMX

Comparisons (floating-point)

Convert SS = single precision SD = double precision

SS -> SD

| miasm.arch.x86.arch.bnd_reg = bs(l=3, cls=(x86_rm_reg_bnd, ), order =1, fname = "reg") |

| miasm.arch.x86.arch.bs_admode16 = bs(l=0, cls=(bs_ad_mode,), mode = 16, fname="fadmode") |

| miasm.arch.x86.arch.bs_admode32 = bs(l=0, cls=(bs_ad_mode,), mode = 32, fname="fadmode") |

| miasm.arch.x86.arch.bs_admode64 = bs(l=0, cls=(bs_ad_mode,), mode = 64, fname="fadmode") |

| miasm.arch.x86.arch.bs_mode64 = bs(l=0, cls=(bs_op_mode64,)) |

| miasm.arch.x86.arch.bs_modeno64 = bs(l=0, cls=(bs_op_modeno64,)) |

| miasm.arch.x86.arch.bs_opmode16 = bs(l=0, cls=(bs_op_mode,), mode = 16, fname="fopmode") |

| miasm.arch.x86.arch.bs_opmode16_no64 = bs(l=0, cls=(bs_op_mode_no64,), mode = 16, fname="fopmode") |

| miasm.arch.x86.arch.bs_opmode32 = bs(l=0, cls=(bs_op_mode,), mode = 32, fname="fopmode") |

| miasm.arch.x86.arch.bs_opmode32_no64 = bs(l=0, cls=(bs_op_mode_no64,), mode = 32, fname="fopmode") |

| miasm.arch.x86.arch.bs_opmode64 = bs(l=0, cls=(bs_op_mode,), mode = 64, fname="fopmode") |

| miasm.arch.x86.arch.BYTE = Literal('BYTE') |

| miasm.arch.x86.arch.cl_or_imm = r08_ecx.parser |

| miasm.arch.x86.arch.COLON = Suppress(":") |

| miasm.arch.x86.arch.cond = bs_mod_name(l=4, fname='cond', mn_mod=cond_list) |

| list miasm.arch.x86.arch.cond_list |

| list miasm.arch.x86.arch.conditional_branch |

| miasm.arch.x86.arch.console_handler = logging.StreamHandler() |

| miasm.arch.x86.arch.crx_info = reg_info_dct(enc2crx) |

| miasm.arch.x86.arch.d_imm = bs(l=0, cls=(bs_cond_imm,), fname="imm") |

| miasm.arch.x86.arch.d_imm64 = bs(l=0, fname="imm64") |

| miasm.arch.x86.arch.d_st = bs(l=0, cls=(x86_reg_st, ), fname='st') |

| list miasm.arch.x86.arch.db_afs_64 = [] |

| tuple miasm.arch.x86.arch.deref_mem = (mem_size + PTR + Optional((base_expr + COLON))+ deref_mem_ad).setParseAction(cb_deref_mem) |

| tuple miasm.arch.x86.arch.deref_mem_ad = (LBRACK + base_expr + RBRACK).setParseAction(cb_deref_base_expr) |

| tuple miasm.arch.x86.arch.deref_ptr = (base_expr + COLON + base_expr).setParseAction(cb_deref_segmoff) |

| miasm.arch.x86.arch.disp = bs(l=0, cls=(bs_cond_disp,), fname = "disp") |

| miasm.arch.x86.arch.drx_info = reg_info_dct(enc2drx) |

| miasm.arch.x86.arch.DWORD = Literal('DWORD') |

| dictionary miasm.arch.x86.arch.enc2crx |

| dictionary miasm.arch.x86.arch.enc2drx |

| miasm.arch.x86.arch.enc2segm = dict((value, key) for key, value in viewitems(segm2enc)) |

| string miasm.arch.x86.arch.f_imm = 'IMM' |

| dictionary miasm.arch.x86.arch.f_imm2size |

| string miasm.arch.x86.arch.f_isad = "AD" |

| string miasm.arch.x86.arch.f_s08 = "S08" |

| string miasm.arch.x86.arch.f_s16 = "S16" |

| string miasm.arch.x86.arch.f_s32 = "S32" |

| string miasm.arch.x86.arch.f_s64 = "S64" |

| string miasm.arch.x86.arch.f_u08 = "U08" |

| string miasm.arch.x86.arch.f_u16 = "U16" |

| string miasm.arch.x86.arch.f_u32 = "U32" |

| string miasm.arch.x86.arch.f_u64 = "U64" |

| miasm.arch.x86.arch.FAR = Suppress('FAR') |

| miasm.arch.x86.arch.fltreg = bs(l=3, cls=(x86_rm_flt, ), order =1, fname = "reg") |

| tuple miasm.arch.x86.arch.gpreg |

| dictionary miasm.arch.x86.arch.invmode = {16: 32, 32: 16} |

| miasm.arch.x86.arch.LBRACK = Suppress("[") |

| miasm.arch.x86.arch.log = logging.getLogger("x86_arch") |

| dictionary miasm.arch.x86.arch.MEMPREFIX2SIZE |

| miasm.arch.x86.arch.mm_reg = bs(l=3, cls=(x86_rm_reg_mm, ), order =1, fname = "reg") |

| miasm.arch.x86.arch.mmreg = bs(l=0, fname="mmreg") |

| miasm.arch.x86.arch.mod = bs(l=2, fname="mod") |

| miasm.arch.x86.arch.msegoff = bs(l=16, cls=(bs_msegoff,), fname="mseg") |

| miasm.arch.x86.arch.MULT = Suppress("*") |

| miasm.arch.x86.arch.no_rex = bs(l=0, fname="no_rex") |

| miasm.arch.x86.arch.no_xmm_pref = bs(l=0, fname="no_xmm_pref") |

| miasm.arch.x86.arch.PLUS = Suppress("+") |

| miasm.arch.x86.arch.pref_66 = bs(l=0, fname="prefixed", default=b"\x66") |

| miasm.arch.x86.arch.pref_f2 = bs(l=0, fname="prefixed", default=b"\xf2") |

| miasm.arch.x86.arch.pref_f3 = bs(l=0, fname="prefixed", default=b"\xf3") |

| miasm.arch.x86.arch.PTR = Suppress('PTR') |

| miasm.arch.x86.arch.QWORD = Literal('QWORD') |

| miasm.arch.x86.arch.RBRACK = Suppress("]") |

| miasm.arch.x86.arch.reg_modrm = bs(l=3, cls=(x86_reg_modrm, ), order =1, fname = "reg") |

| miasm.arch.x86.arch.regnoarg = bs(l=3, default_val="000", order=1, fname="reg") |

| miasm.arch.x86.arch.rel_off = bs(l=0, cls=(bs_rel_off,), fname="off", order=-1) |

| miasm.arch.x86.arch.rel_off08 = bs(l=8, cls=(bs_rel_off08,), fname="off", order=-1) |

| list miasm.arch.x86.arch.repeat_mn |

| dictionary miasm.arch.x86.arch.replace_regs |

| dictionary miasm.arch.x86.arch.replace_regs16 |

| dictionary miasm.arch.x86.arch.replace_regs32 |

| dictionary miasm.arch.x86.arch.replace_regs64 |

| miasm.arch.x86.arch.rm = bs(l=3, fname="rm") |

| miasm.arch.x86.arch.rm_arg = bs(l=0, cls=(x86_rm_arg,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_bnd = bs(l=0, cls=(x86_rm_bnd,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_bnd_m128 = bs(l=0, cls=(x86_rm_bnd_m128,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_bnd_m64 = bs(l=0, cls=(x86_rm_bnd_m64,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_bnd_reg = bs(l=0, cls=(x86_rm_bnd_reg,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_m08 = bs(l=0, cls=(x86_rm_m08,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_m16 = bs(l=0, cls=(x86_rm_m16,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_m64 = bs(l=0, cls=(x86_rm_m64,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_m80 = bs(l=0, cls=(x86_rm_m80,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_mm_m64 = bs(l=0, cls=(x86_rm_mm_m64,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_mm_reg = bs(l=0, cls=(x86_rm_mm_reg,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_reg_m08 = bs(l=0, cls=(x86_rm_reg_m08,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_reg_m16 = bs(l=0, cls=(x86_rm_reg_m16,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_sxd = bs(l=0, cls=(x86_rm_sxd,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_xmm = bs(l=0, cls=(x86_rm_xmm,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_xmm_m128 = bs(l=0, cls=(x86_rm_xmm_m128,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_xmm_m32 = bs(l=0, cls=(x86_rm_xmm_m32,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_xmm_m64 = bs(l=0, cls=(x86_rm_xmm_m64,), fname='rmarg') |

| miasm.arch.x86.arch.rm_arg_xmm_reg = bs(l=0, cls=(x86_rm_xmm_reg,), fname='rmarg') |

| miasm.arch.x86.arch.rm_mem = bs(l=0, cls=(x86_rm_mem,), fname='rmarg') |

| miasm.arch.x86.arch.rm_mem_far = bs(l=0, cls=(x86_rm_mem_far,), fname='rmarg') |

| tuple miasm.arch.x86.arch.rmarg |

| miasm.arch.x86.arch.rmreg = bs(l=3, cls=(x86_rm_reg, ), order =1, fname = "reg") |

| miasm.arch.x86.arch.s3264 = bs(l=32, cls=(x86_s32to64, x86_arg)) |

| miasm.arch.x86.arch.sd = bs(l=1, fname="sd") |

| miasm.arch.x86.arch.se = bs(l=1, fname="se") |

| miasm.arch.x86.arch.segm = bs(l=3, cls=(x86_rm_segm, ), order =1, fname = "reg") |

| dictionary miasm.arch.x86.arch.segm2enc = {CS: 1, SS: 2, DS: 3, ES: 4, FS: 5, GS: 6} |

| miasm.arch.x86.arch.segm_info = reg_info_dct(enc2segm) |

| list miasm.arch.x86.arch.sib_64_s08_ebp = [] |

| miasm.arch.x86.arch.sib_base = bs(l=3, cls=(bs_cond_index,), fname = "sib_base") |

| miasm.arch.x86.arch.sib_index = bs(l=3, cls=(bs_cond_index,), fname = "sib_index") |

| miasm.arch.x86.arch.sib_scale = bs(l=2, cls=(bs_cond_scale,), fname = "sib_scale") |

| dictionary miasm.arch.x86.arch.size2gpregs |

| miasm.arch.x86.arch.SIZE2MEMPREFIX = dict((value, key) for key, value in viewitems(MEMPREFIX2SIZE)) |

| miasm.arch.x86.arch.stk = bs(l=0, fname="stk") |

| miasm.arch.x86.arch.swapargs = bs_swapargs(l=1, fname="swap", mn_mod=list(range(1 << 1))) |

| miasm.arch.x86.arch.sx = bs(l=0, fname="sx") |

| miasm.arch.x86.arch.sxd = bs(l=0, fname="sx") |

| miasm.arch.x86.arch.TBYTE = Literal('TBYTE') |

| miasm.arch.x86.arch.u08_3 = bs(l=0, cls=(x86_imm_fix_08, x86_arg), ival = 3) |

| list miasm.arch.x86.arch.unconditional_branch = ['JMP', 'JMPF'] |

| miasm.arch.x86.arch.w8 = bs(l=1, fname="w8") |

| miasm.arch.x86.arch.wd = bs(l=1, fname="wd") |

| miasm.arch.x86.arch.WORD = Literal('WORD') |

| miasm.arch.x86.arch.xmm_reg = bs(l=3, cls=(x86_rm_reg_xmm, ), order =1, fname = "reg") |

| miasm.arch.x86.arch.xmmreg = bs(l=0, fname="xmmreg") |

| miasm.arch.x86.arch.XMMWORD = Literal('XMMWORD') |