#include <JitCore_aarch64.h>

◆ A0

◆ A1

◆ A2

◆ A3

◆ ac

◆ af

◆ AT

◆ BADINSTR

| uint32_t vm_cpu::BADINSTR |

◆ BADINSTRP

| uint32_t vm_cpu::BADINSTRP |

◆ BADVADDR

| uint32_t vm_cpu::BADVADDR |

◆ bp_num

◆ CAUSE

◆ CCFG

◆ cf [1/2]

◆ cf [2/2]

◆ CFG

◆ cond

◆ CONFIG

◆ CONFIG1

◆ CONFIG2

◆ CONFIG3

◆ CONFIG4

◆ CONFIG5

◆ CONTEXT

◆ CONTEXTCONFIG

| uint32_t vm_cpu::CONTEXTCONFIG |

◆ COUNT

◆ CPR0_1

◆ CPR0_10

◆ CPR0_100

| uint32_t vm_cpu::CPR0_100 |

◆ CPR0_101

| uint32_t vm_cpu::CPR0_101 |

◆ CPR0_102

| uint32_t vm_cpu::CPR0_102 |

◆ CPR0_103

| uint32_t vm_cpu::CPR0_103 |

◆ CPR0_105

| uint32_t vm_cpu::CPR0_105 |

◆ CPR0_106

| uint32_t vm_cpu::CPR0_106 |

◆ CPR0_107

| uint32_t vm_cpu::CPR0_107 |

◆ CPR0_108

| uint32_t vm_cpu::CPR0_108 |

◆ CPR0_109

| uint32_t vm_cpu::CPR0_109 |

◆ CPR0_11

◆ CPR0_110

| uint32_t vm_cpu::CPR0_110 |

◆ CPR0_111

| uint32_t vm_cpu::CPR0_111 |

◆ CPR0_113

| uint32_t vm_cpu::CPR0_113 |

◆ CPR0_114

| uint32_t vm_cpu::CPR0_114 |

◆ CPR0_115

| uint32_t vm_cpu::CPR0_115 |

◆ CPR0_116

| uint32_t vm_cpu::CPR0_116 |

◆ CPR0_117

| uint32_t vm_cpu::CPR0_117 |

◆ CPR0_118

| uint32_t vm_cpu::CPR0_118 |

◆ CPR0_119

| uint32_t vm_cpu::CPR0_119 |

◆ CPR0_12

◆ CPR0_122

| uint32_t vm_cpu::CPR0_122 |

◆ CPR0_123

| uint32_t vm_cpu::CPR0_123 |

◆ CPR0_124

| uint32_t vm_cpu::CPR0_124 |

◆ CPR0_125

| uint32_t vm_cpu::CPR0_125 |

◆ CPR0_126

| uint32_t vm_cpu::CPR0_126 |

◆ CPR0_127

| uint32_t vm_cpu::CPR0_127 |

◆ CPR0_13

◆ CPR0_134

| uint32_t vm_cpu::CPR0_134 |

◆ CPR0_135

| uint32_t vm_cpu::CPR0_135 |

◆ CPR0_136

| uint32_t vm_cpu::CPR0_136 |

◆ CPR0_137

| uint32_t vm_cpu::CPR0_137 |

◆ CPR0_138

| uint32_t vm_cpu::CPR0_138 |

◆ CPR0_139

| uint32_t vm_cpu::CPR0_139 |

◆ CPR0_14

◆ CPR0_140

| uint32_t vm_cpu::CPR0_140 |

◆ CPR0_141

| uint32_t vm_cpu::CPR0_141 |

◆ CPR0_142

| uint32_t vm_cpu::CPR0_142 |

◆ CPR0_143

| uint32_t vm_cpu::CPR0_143 |

◆ CPR0_144

| uint32_t vm_cpu::CPR0_144 |

◆ CPR0_145

| uint32_t vm_cpu::CPR0_145 |

◆ CPR0_146

| uint32_t vm_cpu::CPR0_146 |

◆ CPR0_147

| uint32_t vm_cpu::CPR0_147 |

◆ CPR0_148

| uint32_t vm_cpu::CPR0_148 |

◆ CPR0_149

| uint32_t vm_cpu::CPR0_149 |

◆ CPR0_15

◆ CPR0_150

| uint32_t vm_cpu::CPR0_150 |

◆ CPR0_151

| uint32_t vm_cpu::CPR0_151 |

◆ CPR0_153

| uint32_t vm_cpu::CPR0_153 |

◆ CPR0_154

| uint32_t vm_cpu::CPR0_154 |

◆ CPR0_155

| uint32_t vm_cpu::CPR0_155 |

◆ CPR0_156

| uint32_t vm_cpu::CPR0_156 |

◆ CPR0_157

| uint32_t vm_cpu::CPR0_157 |

◆ CPR0_158

| uint32_t vm_cpu::CPR0_158 |

◆ CPR0_159

| uint32_t vm_cpu::CPR0_159 |

◆ CPR0_160

| uint32_t vm_cpu::CPR0_160 |

◆ CPR0_161

| uint32_t vm_cpu::CPR0_161 |

◆ CPR0_162

| uint32_t vm_cpu::CPR0_162 |

◆ CPR0_163

| uint32_t vm_cpu::CPR0_163 |

◆ CPR0_164

| uint32_t vm_cpu::CPR0_164 |

◆ CPR0_165

| uint32_t vm_cpu::CPR0_165 |

◆ CPR0_166

| uint32_t vm_cpu::CPR0_166 |

◆ CPR0_167

| uint32_t vm_cpu::CPR0_167 |

◆ CPR0_168

| uint32_t vm_cpu::CPR0_168 |

◆ CPR0_169

| uint32_t vm_cpu::CPR0_169 |

◆ CPR0_17

◆ CPR0_170

| uint32_t vm_cpu::CPR0_170 |

◆ CPR0_171

| uint32_t vm_cpu::CPR0_171 |

◆ CPR0_172

| uint32_t vm_cpu::CPR0_172 |

◆ CPR0_173

| uint32_t vm_cpu::CPR0_173 |

◆ CPR0_174

| uint32_t vm_cpu::CPR0_174 |

◆ CPR0_175

| uint32_t vm_cpu::CPR0_175 |

◆ CPR0_176

| uint32_t vm_cpu::CPR0_176 |

◆ CPR0_177

| uint32_t vm_cpu::CPR0_177 |

◆ CPR0_178

| uint32_t vm_cpu::CPR0_178 |

◆ CPR0_179

| uint32_t vm_cpu::CPR0_179 |

◆ CPR0_18

◆ CPR0_180

| uint32_t vm_cpu::CPR0_180 |

◆ CPR0_181

| uint32_t vm_cpu::CPR0_181 |

◆ CPR0_182

| uint32_t vm_cpu::CPR0_182 |

◆ CPR0_183

| uint32_t vm_cpu::CPR0_183 |

◆ CPR0_184

| uint32_t vm_cpu::CPR0_184 |

◆ CPR0_185

| uint32_t vm_cpu::CPR0_185 |

◆ CPR0_186

| uint32_t vm_cpu::CPR0_186 |

◆ CPR0_187

| uint32_t vm_cpu::CPR0_187 |

◆ CPR0_188

| uint32_t vm_cpu::CPR0_188 |

◆ CPR0_189

| uint32_t vm_cpu::CPR0_189 |

◆ CPR0_19

◆ CPR0_190

| uint32_t vm_cpu::CPR0_190 |

◆ CPR0_191

| uint32_t vm_cpu::CPR0_191 |

◆ CPR0_192

| uint32_t vm_cpu::CPR0_192 |

◆ CPR0_193

| uint32_t vm_cpu::CPR0_193 |

◆ CPR0_194

| uint32_t vm_cpu::CPR0_194 |

◆ CPR0_195

| uint32_t vm_cpu::CPR0_195 |

◆ CPR0_196

| uint32_t vm_cpu::CPR0_196 |

◆ CPR0_197

| uint32_t vm_cpu::CPR0_197 |

◆ CPR0_198

| uint32_t vm_cpu::CPR0_198 |

◆ CPR0_199

| uint32_t vm_cpu::CPR0_199 |

◆ CPR0_2

◆ CPR0_20

◆ CPR0_200

| uint32_t vm_cpu::CPR0_200 |

◆ CPR0_201

| uint32_t vm_cpu::CPR0_201 |

◆ CPR0_202

| uint32_t vm_cpu::CPR0_202 |

◆ CPR0_203

| uint32_t vm_cpu::CPR0_203 |

◆ CPR0_204

| uint32_t vm_cpu::CPR0_204 |

◆ CPR0_205

| uint32_t vm_cpu::CPR0_205 |

◆ CPR0_206

| uint32_t vm_cpu::CPR0_206 |

◆ CPR0_207

| uint32_t vm_cpu::CPR0_207 |

◆ CPR0_208

| uint32_t vm_cpu::CPR0_208 |

◆ CPR0_209

| uint32_t vm_cpu::CPR0_209 |

◆ CPR0_21

◆ CPR0_210

| uint32_t vm_cpu::CPR0_210 |

◆ CPR0_211

| uint32_t vm_cpu::CPR0_211 |

◆ CPR0_212

| uint32_t vm_cpu::CPR0_212 |

◆ CPR0_213

| uint32_t vm_cpu::CPR0_213 |

◆ CPR0_214

| uint32_t vm_cpu::CPR0_214 |

◆ CPR0_215

| uint32_t vm_cpu::CPR0_215 |

◆ CPR0_216

| uint32_t vm_cpu::CPR0_216 |

◆ CPR0_217

| uint32_t vm_cpu::CPR0_217 |

◆ CPR0_218

| uint32_t vm_cpu::CPR0_218 |

◆ CPR0_219

| uint32_t vm_cpu::CPR0_219 |

◆ CPR0_22

◆ CPR0_220

| uint32_t vm_cpu::CPR0_220 |

◆ CPR0_221

| uint32_t vm_cpu::CPR0_221 |

◆ CPR0_222

| uint32_t vm_cpu::CPR0_222 |

◆ CPR0_223

| uint32_t vm_cpu::CPR0_223 |

◆ CPR0_224

| uint32_t vm_cpu::CPR0_224 |

◆ CPR0_225

| uint32_t vm_cpu::CPR0_225 |

◆ CPR0_226

| uint32_t vm_cpu::CPR0_226 |

◆ CPR0_227

| uint32_t vm_cpu::CPR0_227 |

◆ CPR0_228

| uint32_t vm_cpu::CPR0_228 |

◆ CPR0_229

| uint32_t vm_cpu::CPR0_229 |

◆ CPR0_23

◆ CPR0_230

| uint32_t vm_cpu::CPR0_230 |

◆ CPR0_231

| uint32_t vm_cpu::CPR0_231 |

◆ CPR0_232

| uint32_t vm_cpu::CPR0_232 |

◆ CPR0_233

| uint32_t vm_cpu::CPR0_233 |

◆ CPR0_234

| uint32_t vm_cpu::CPR0_234 |

◆ CPR0_235

| uint32_t vm_cpu::CPR0_235 |

◆ CPR0_236

| uint32_t vm_cpu::CPR0_236 |

◆ CPR0_237

| uint32_t vm_cpu::CPR0_237 |

◆ CPR0_238

| uint32_t vm_cpu::CPR0_238 |

◆ CPR0_239

| uint32_t vm_cpu::CPR0_239 |

◆ CPR0_240

| uint32_t vm_cpu::CPR0_240 |

◆ CPR0_241

| uint32_t vm_cpu::CPR0_241 |

◆ CPR0_242

| uint32_t vm_cpu::CPR0_242 |

◆ CPR0_243

| uint32_t vm_cpu::CPR0_243 |

◆ CPR0_244

| uint32_t vm_cpu::CPR0_244 |

◆ CPR0_245

| uint32_t vm_cpu::CPR0_245 |

◆ CPR0_246

| uint32_t vm_cpu::CPR0_246 |

◆ CPR0_247

| uint32_t vm_cpu::CPR0_247 |

◆ CPR0_248

| uint32_t vm_cpu::CPR0_248 |

◆ CPR0_249

| uint32_t vm_cpu::CPR0_249 |

◆ CPR0_25

◆ CPR0_26

◆ CPR0_27

◆ CPR0_28

◆ CPR0_29

◆ CPR0_3

◆ CPR0_30

◆ CPR0_31

◆ CPR0_34

◆ CPR0_35

◆ CPR0_36

◆ CPR0_37

◆ CPR0_38

◆ CPR0_39

◆ CPR0_4

◆ CPR0_49

◆ CPR0_5

◆ CPR0_50

◆ CPR0_51

◆ CPR0_52

◆ CPR0_53

◆ CPR0_55

◆ CPR0_56

◆ CPR0_57

◆ CPR0_58

◆ CPR0_59

◆ CPR0_6

◆ CPR0_60

◆ CPR0_61

◆ CPR0_62

◆ CPR0_63

◆ CPR0_67

◆ CPR0_68

◆ CPR0_69

◆ CPR0_7

◆ CPR0_70

◆ CPR0_71

◆ CPR0_73

◆ CPR0_74

◆ CPR0_75

◆ CPR0_76

◆ CPR0_77

◆ CPR0_78

◆ CPR0_79

◆ CPR0_81

◆ CPR0_82

◆ CPR0_83

◆ CPR0_84

◆ CPR0_85

◆ CPR0_86

◆ CPR0_87

◆ CPR0_88

◆ CPR0_89

◆ CPR0_9

◆ CPR0_90

◆ CPR0_91

◆ CPR0_92

◆ CPR0_93

◆ CPR0_94

◆ CPR0_95

◆ CPR0_96

◆ CPR0_97

◆ CPR0_98

◆ CPR0_99

◆ cpuoff

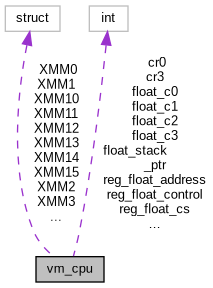

◆ cr0

◆ cr3

◆ CS

◆ DBG

◆ DEPC

◆ df

◆ DS

◆ EBASE

◆ ENTRYHI

◆ ENTRYLO0

| uint32_t vm_cpu::ENTRYLO0 |

◆ ENTRYLO1

| uint32_t vm_cpu::ENTRYLO1 |

◆ EPC

◆ ES

◆ EXC

◆ exception_flags [1/2]

| uint32_t vm_cpu::exception_flags |

◆ exception_flags [2/2]

| uint64_t vm_cpu::exception_flags |

◆ F0

◆ F1

◆ F10

◆ F11

◆ F12

◆ F13

◆ F14

◆ F15

◆ F16

◆ F17

◆ F18

◆ F19

◆ F2

◆ F20

◆ F21

◆ F22

◆ F23

◆ F24

◆ F25

◆ F26

◆ F27

◆ F28

◆ F29

◆ F3

◆ F30

◆ F31

◆ F4

◆ F5

◆ F6

◆ F7

◆ F8

◆ F9

◆ float_c0

| unsigned int vm_cpu::float_c0 |

◆ float_c1

| unsigned int vm_cpu::float_c1 |

◆ float_c2

| unsigned int vm_cpu::float_c2 |

◆ float_c3

| unsigned int vm_cpu::float_c3 |

◆ float_st0

| uint64_t vm_cpu::float_st0 |

◆ float_st1

| uint64_t vm_cpu::float_st1 |

◆ float_st2

| uint64_t vm_cpu::float_st2 |

◆ float_st3

| uint64_t vm_cpu::float_st3 |

◆ float_st4

| uint64_t vm_cpu::float_st4 |

◆ float_st5

| uint64_t vm_cpu::float_st5 |

◆ float_st6

| uint64_t vm_cpu::float_st6 |

◆ float_st7

| uint64_t vm_cpu::float_st7 |

◆ float_stack_ptr

| unsigned int vm_cpu::float_stack_ptr |

◆ FP

◆ FS

◆ ge0

◆ ge1

◆ ge2

◆ ge3

◆ gie

◆ GP

◆ GS

◆ HI

◆ i_d

◆ i_f

◆ ID

◆ in_erepeat

| uint32_t vm_cpu::in_erepeat |

◆ INDEX

◆ interrupt_num

| uint32_t vm_cpu::interrupt_num |

◆ iopl_f

◆ is_repeat_end

| uint32_t vm_cpu::is_repeat_end |

◆ K0

◆ K1

◆ KSCRATCH0

| uint32_t vm_cpu::KSCRATCH0 |

◆ KSCRATCH1

| uint32_t vm_cpu::KSCRATCH1 |

◆ KSCRATCH2

| uint32_t vm_cpu::KSCRATCH2 |

◆ KSCRATCH3

| uint32_t vm_cpu::KSCRATCH3 |

◆ KSCRATCH4

| uint32_t vm_cpu::KSCRATCH4 |

◆ KSCRATCH5

| uint32_t vm_cpu::KSCRATCH5 |

◆ last_addr

| uint32_t vm_cpu::last_addr |

◆ LO

◆ LP

◆ LR [1/2]

◆ LR [2/2]

◆ MB0

◆ MB1

◆ ME0

◆ ME1

◆ MM0

◆ MM1

◆ MM2

◆ MM3

◆ MM4

◆ MM5

◆ MM6

◆ MM7

◆ my_tick

◆ nf [1/2]

◆ nf [2/2]

◆ NPC

◆ nt

◆ of [1/2]

◆ of [2/2]

◆ OPT

◆ osc

◆ PAGEGRAIN

| uint32_t vm_cpu::PAGEGRAIN |

◆ PAGEMASK

| uint32_t vm_cpu::PAGEMASK |

◆ PC [1/2]

◆ PC [2/2]

◆ PC_end

◆ PC_FETCH

| uint32_t vm_cpu::PC_FETCH |

◆ pf

◆ PRID

◆ PSW

◆ PWBASE

◆ PWCTL

◆ PWFIELD

◆ PWSIZE

◆ R0

◆ R1

◆ R10 [1/2]

◆ R10 [2/2]

◆ R11 [1/2]

◆ R11 [2/2]

◆ R12 [1/2]

◆ R12 [2/2]

◆ R13 [1/2]

◆ R13 [2/2]

◆ R14 [1/2]

◆ R14 [2/2]

◆ R15 [1/2]

◆ R15 [2/2]

◆ R2

◆ R3

◆ R4

◆ R5

◆ R6

◆ R7

◆ R8 [1/2]

◆ R8 [2/2]

◆ R9 [1/2]

◆ R9 [2/2]

◆ R_HI

◆ R_LO

◆ RA

◆ RANDOM

◆ RAX

◆ RBP

◆ RBX

◆ RCFG

◆ RCX

◆ RDI

◆ RDX

◆ reg_float_address

| unsigned int vm_cpu::reg_float_address |

◆ reg_float_control

| unsigned int vm_cpu::reg_float_control |

◆ reg_float_cs

| unsigned int vm_cpu::reg_float_cs |

◆ reg_float_ds

| unsigned int vm_cpu::reg_float_ds |

◆ reg_float_eip

| unsigned int vm_cpu::reg_float_eip |

◆ res

◆ reserve

◆ reserve_address

| uint32_t vm_cpu::reserve_address |

◆ rf

◆ RIP

◆ RPB

◆ RPC

◆ RPC_current

| uint32_t vm_cpu::RPC_current |

◆ RPE

◆ RPE_instr_count

| uint32_t vm_cpu::RPE_instr_count |

◆ RSI

◆ RSP

◆ S0

◆ S1

◆ S10

◆ S11

◆ S2

◆ S22

◆ S29

◆ S3

◆ S30

◆ S31

◆ S32

◆ S4

◆ S5

◆ S6

◆ S7

◆ S9

◆ SAR

◆ scg0

◆ scg1

◆ SEGCTL0

◆ SEGCTL1

◆ SEGCTL2

◆ segm_base

| uint64_t vm_cpu::segm_base[0x10000] |

◆ SP [1/2]

◆ SP [2/2]

◆ spr_access

| uint32_t vm_cpu::spr_access |

◆ SS

◆ T0

◆ T1

◆ T2

◆ T3

◆ T4

◆ T5

◆ T6

◆ T7

◆ T8

◆ T9

◆ take_jmp

| uint32_t vm_cpu::take_jmp |

◆ tf

◆ TMP

◆ TP

◆ tsc

◆ V0

◆ V1

◆ vif

◆ vip

◆ vm

◆ WATCHHI

◆ WIRED

◆ X0

◆ X1

◆ X10

◆ X11

◆ X12

◆ X13

◆ X14

◆ X15

◆ X16

◆ X17

◆ X18

◆ X19

◆ X2

◆ X20

◆ X21

◆ X22

◆ X23

◆ X24

◆ X25

◆ X26

◆ X27

◆ X28

◆ X29

◆ X3

◆ X4

◆ X5

◆ X6

◆ X7

◆ X8

◆ X9

◆ XMM0

◆ XMM1

◆ XMM10

◆ XMM11

◆ XMM12

◆ XMM13

◆ XMM14

◆ XMM15

◆ XMM2

◆ XMM3

◆ XMM4

◆ XMM5

◆ XMM6

◆ XMM7

◆ XMM8

◆ XMM9

◆ ZERO

◆ zf [1/2]

◆ zf [2/2]

The documentation for this struct was generated from the following files:

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/jitter/arch/JitCore_aarch64.h

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/jitter/arch/JitCore_arm.h

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/jitter/arch/JitCore_mep.h

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/jitter/arch/JitCore_mips32.h

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/jitter/arch/JitCore_msp430.h

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/jitter/arch/JitCore_ppc32.h

- /home/serpilliere/projet/test_doc_miasm/miasm/miasm/jitter/arch/JitCore_x86.h